## **Electrical Engineering**

Department at HES-SO: Systèmes industriels

# Mains driven transmitter & portable receiver for visible light communication Indoor positioning

Master's thesis to obtain the degree of Master in Industrial Sciences: Electronics-ICT offered by: Jelle Smets and Rob Holvoet

Promotor: Mr. François Corthay Academic year: 2012 - 2013

# **Acknowledgements**

We could not accomplish this master's thesis without the help of lots of people. Hereby we would like to thank all those people who helped us to bring this thesis work to a good end.

Special thanks to François Corthay as our promotor at HES-SO Valais/Wallis in Sion. For the good advice he gave us, and to encourage us to try different ways to do things and look for new/other solutions. His close and enthusiast accompaniment was a great help for us.

We got a great help from Olivier Walpen and Steve Gallay who gave us advice about lots of different things and did the routing and the etching of our boards, what made it possible to move on faster.

Médard Rieder helped us to design an anti-aliasing filter before the ADC. He recommended a program where you can easily design a filter with a certain cut-off frequency. He also shared his experience about the problems we had with the ADC (sampling noise, input spikes...).

We would also like to thank Oliver Gubler, Silvan Zahno and Darko Petrovic for there enthusiastic help whenever we needed it. Silvan Zahno helped us when we had problems with the Ethernet code.

Many thanks to Didier Blatter for the help, advice and information about designing the transformer circuit.

For information and advice about LEDs and photodiodes we could count on the help from Frederic Truffer.

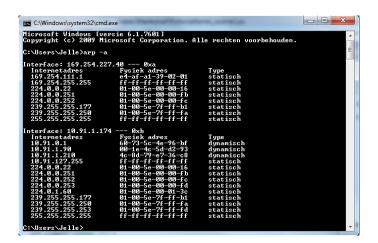

Dominique Gabioud helped us when we had problems to send a UDP packet from the PC to the FPGA. We had to add manually the IP address and MAC address of the FPGA in the ARP table so we could send messages to the FPGA.

The HES-SO Valais/Wallis in Sion was a great school to do research and we got every support we needed both in terms of information, help, enthusiasm, advice or provision of professional equipment.

All of this wouldn't be possible if we didn't found a place in Sion to sleep, cook or relax. We got a warm welcome from the family Dayer who shared their house with us and showed us around.

# **Abstract (English)**

Names: Rob Holvoet, Jelle Smets

Contact: robholvoet@hotmail.com, jelle.smets@hotmail.com

**Title:** Mains driven transmitter and portable receiver for visible light communication: indoor positioning.

The possibilities of Visible Light Communication (VLC) for indoor positioning are being studied in this work. The placement of several LEDs on the ceiling can have a dual purpose: first, the lighting in the room and second the transmission of binary sequences. The binary sequences are send at a high frequency and are thus invisible for the human eye. A light receiving device can detect these sequences and measure their amplitude. The different amplitudes are in function of the distances. This property allows to calculate the position of the receiver in the room.

For the sending part, a stand-alone prototype is created to be connected to the mains in a room. A transformer circuit (Flyback) is used to drive the led. Two different possibilities to implement the binary sequence in the emitted light are investigated. Once by using the switch of the transformer circuit and once by placing a switch in series with the LED. An FPGA is used to generate the binary sequence.

For the receiving part, a photodiode is used with an analog circuitry to detect, filter and amplify the transmitted light sequences. An ADC is used to digitalize the received information. This makes it possible to send the data to a digital device. Software can then be used to process the data.

**Key words:** Visible Light Communication (VLC), indoor positioning, flyback converter, optical receiver, correlation filter.

# **Abstract (Français)**

Noms: Rob Holvoet, Jelle Smets

Contact: robholvoet@hotmail.com, jelle.smets@hotmail.com

**Titre:** Émetteur alimenté par le secteur et récepteur portable pour la communication par la lumière visible: détermination du placement à l'intérieure.

Les possibilités de la communication par la lumière visible (Visible Light Communication, VLC) ont été étudiées pour le calcul de position à l'intérieur d'une pièce. La fixation de plusieurs lampes à LEDs au plafond peut avoir deux buts: premièrement, l'éclairage dans une chambre et deuxièmement la transmission de séquences binaires. Les séquences binaires sont envoyées à une haute fréquence et sont donc invisibles pour les yeux humains. Un appareil optique peut détecter les séquences et mesurer leurs amplitudes. Les amplitudes différentes sont une fonction des distances. Cette propriété permet de calculer la position du récepteur dans la pièce.

Pour l'émetteur, un prototype autonome a été développé. Il est alimenté par le secteur. Un transformateur est utilisé pour piloter la LED. Deux possibilités différentes pour implémenter la sequence binaire sur la lumière envoyée ont été examinées: la première consiste à utiliser l'interrupteur du circuit à transformateur "flyback" et l'autre à plaçer un interrupteur en série avec le LED. Un circuit programmable FPGA est utilisé pour générer la séquence binaire.

Pour ce qui est du récepteur, une photodiode est utilisée avec un circuit analogique pour détecter, filtrer et amplifier la sequence binaire envoyée. Un convertisseur A/D est utilisé pour numériser l'information reçue. Il est alors possible d'envoyer ces données à un appareil numérique où un programme peut servir à traiter ces données.

**Mots-clés:** communication par la lumière visible, détermination du placement à l'intérieure, convertisseur flyback, récepteur optique, filtre de corrélation.

# **Abstract (Nederlands)**

Namen: Rob Holvoet, Jelle Smets

Contact: robholvoet@hotmail.com, jelle.smets@hotmail.com

**Titel:** Verzender op netspanning en draagbare ontvanger voor communicatie met zichtbaar light: Indoor positiebepaling.

In deze paper zullen de mogelijkheden bestudeerd worden van communicatie met zichtbaar licht (Visible Light Communication, VLC) voor indoor positiebepaling. Het plaatsen van LEDs aan het plafond heeft hier een dubbele functie: enerzijds de verlichting van de ruimte en anderzijds het verzenden van binaire sequenties. De binaire sequenties worden verzonden op een hoge frequentie en zijn dus niet waarneembaar door het menselijke oog. Een optische ontvanger kan deze sequenties detecteren en hun amplitude bepalen. De verschillende amplitudes zijn namelijk in functie van de afstanden. Deze eigenschap laat toe om de positie te bepalen van een ontvanger in een kamer.

Als zender wordt een autonoom prototype gemaakt die onmiddellijk verbonden wordt op de netspanning. Voor het voeden van de led wordt er gebruik gemaakt van een transformator circuit (Flyback). Twee verschillende mogelijkheden worden bekeken om de binaire sequenties te implementeren in het uitgestraalde licht. De mogelijkheid om de schakelaar van de transformator circuit zelf te gebruiken wordt enerzijds onderzocht en anderzijds wordt de mogelijkheid bekeken om de schakelaar in serie te zetten met de LED. Er wordt gebruik gemaakt van een FPGA om de binaire sequenties te genereren.

Wat de ontvanger betreft wordt gebruik gemaakt van een fotodiode samen met een analoog circuit om de verzonden licht sequenties te detecteren, filteren en versterken. Een ADC wordt gebruikt om de ontvangen informatie te digitaliseren. Dit maakt het mogelijk om de data te verzenden naar een digitaal apparaat. Software kan dan gebruikt worden om de data te verwerken.

**Trefwoorden:** communicatie met zichtbaar light, indoor positiebepaling, flyback converter, optische ontvanger, correlatie filter

# **Contents**

| 1 | Intr | oduction                                        | 1  |

|---|------|-------------------------------------------------|----|

| 2 | Prep | paration and Research                           | 3  |

|   | 2.1  | Choice of emitting LED and receiving photodiode | 3  |

|   |      | 2.1.1 Introduction                              | 3  |

|   |      | 2.1.2 LED                                       | 3  |

|   |      | 2.1.3 Photodiode                                | 5  |

|   |      | 2.1.4 Conclusion                                | 10 |

| 3 | LED  | driver circuit                                  | 12 |

|   | 3.1  | Introduction                                    | 12 |

|   | 3.2  | Power Supply Topologies                         | 13 |

|   | 3.3  | Flyback Converter                               | 13 |

|   | 3.4  | LFSR                                            | 15 |

|   |      | 3.4.1 First tests                               | 15 |

|   |      | 3.4.2 Final LFSR                                | 15 |

|   | 3.5  | LED Heatsink                                    | 15 |

|   | 3.6  | Testing circuit 1                               | 16 |

|   |      | 3.6.1 Tests                                     | 17 |

|   | 3.7  | Testing circuit 2                               | 18 |

|   |      | 3.7.1 Twisted pair cable                        | 18 |

|   |      | 3.7.2 Tests                                     | 19 |

|   |      | 3.7.3 VHDL of sender FPGA                       | 19 |

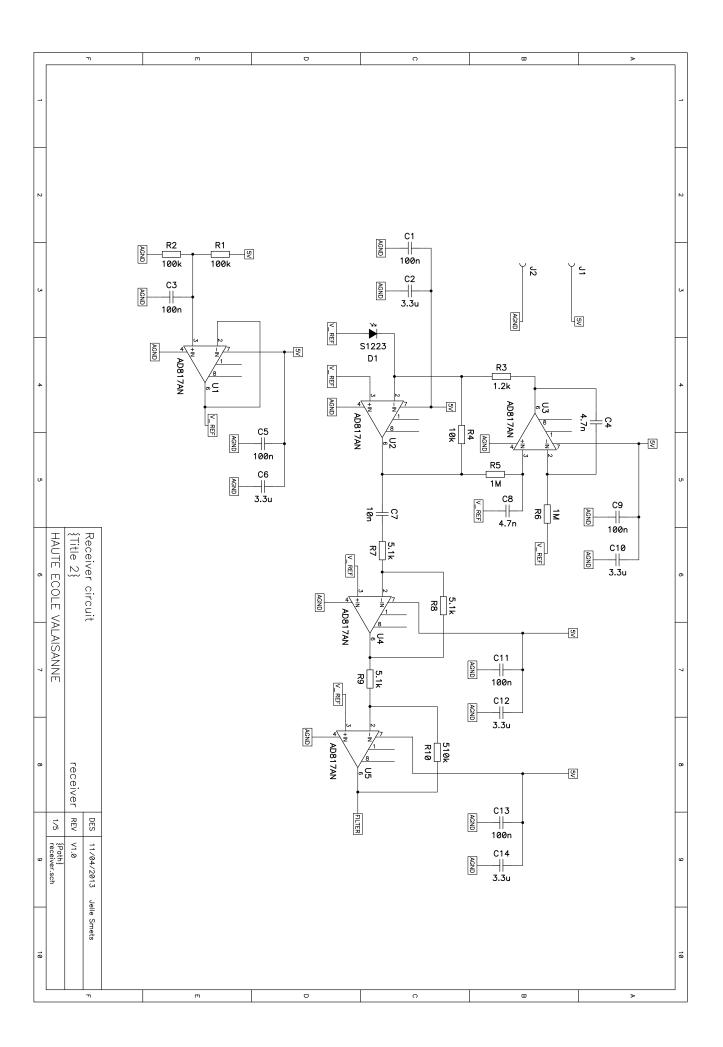

| 4 | The  | receiver circuit                                | 21 |

|   | 4.1  | Introduction                                    | 21 |

|   | 4.2  | Power supply                                    | 22 |

|   | 4.3  | Current-voltage converter                       | 23 |

|   | 4.4               | Ambient light filter                               | 24             |

|---|-------------------|----------------------------------------------------|----------------|

|   | 4.5               | Amplifier                                          | 28             |

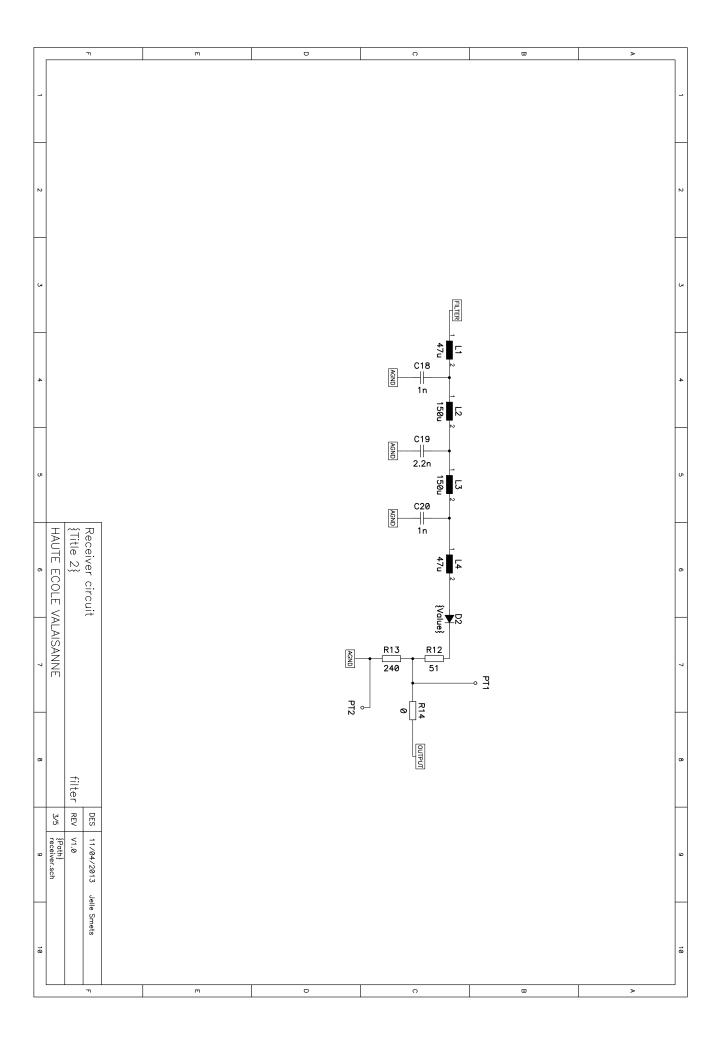

|   | 4.6               | Anti-aliasing filter                               | 28             |

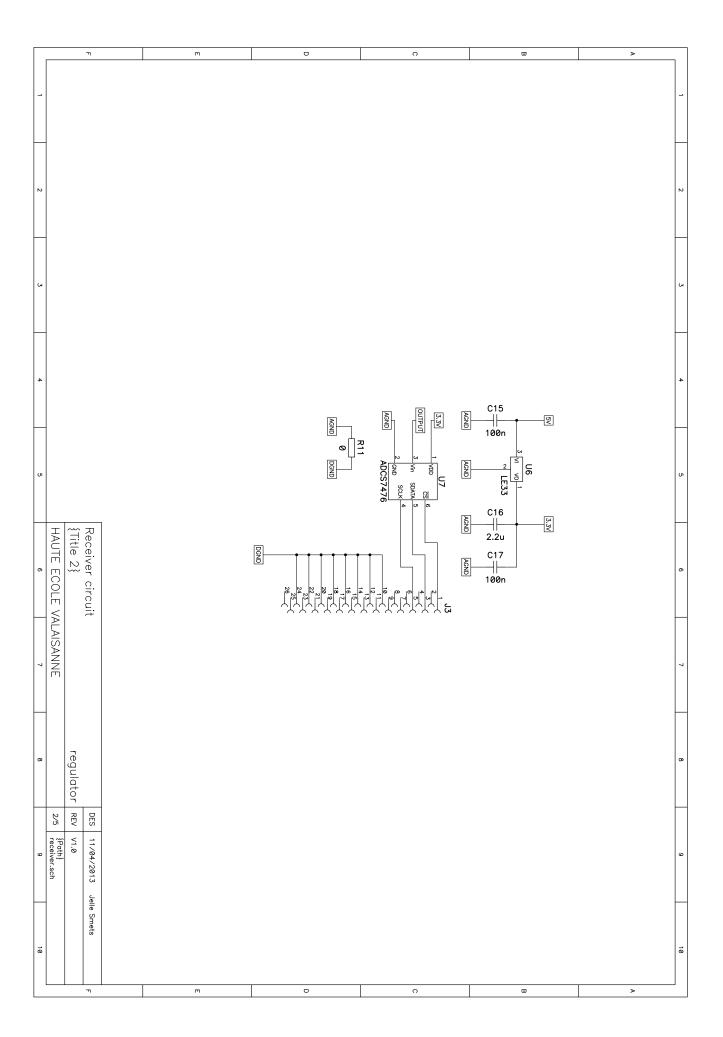

|   | 4.7               | ADC                                                | 32             |

| 5 | Con               | nection to the PC                                  | 37             |

|   | 5.1               | Introduction                                       | 37             |

|   | 5.2               | Structure Ethernet communication                   | 37             |

| 6 | Proc              | cessing with Python                                | 42             |

|   | 6.1               | Receiving the data                                 | 42             |

|   | 6.2               | Processing the data                                | 44             |

|   | 6.3               | Positioning                                        | 48             |

|   |                   | 6.3.1 Radius calculation                           | 48             |

|   |                   | 6.3.2 Position calculation                         | 50             |

|   |                   | 6.3.3 Data Transmission                            | 52             |

| 7 | Resu              | ılt                                                | 53             |

| 8 | Futu              | ire work                                           | 54             |

| A | List              | of Main Switch Mode Power Supply (SMPS) Topologies | 57             |

| В | Calc              | culations to determine the needed heat sink        | 59             |

| C | Aml               | pient light rejection circuit                      | 61             |

| D | Sim               | ulations                                           | 66             |

|   | D.1               | ADC                                                | 66             |

|   | D.2               |                                                    | 68             |

| E |                   |                                                    |                |

|   | Test              | s of sending circuit                               | 70             |

|   | Tests             |                                                    | <b>70</b> 70   |

|   |                   | s of sending circuit                               |                |

|   | E.1               | s of sending circuit  Results Test 1 of circuit 1  | 70             |

|   | E.1<br>E.2        | s of sending circuit  Results Test 1 of circuit 1  | 70<br>70       |

|   | E.1<br>E.2<br>E.3 | Results Test 1 of circuit 1                        | 70<br>70<br>70 |

| I | Code | e      |                                              |   |     |   |       |   |   |     |   | 113 |

|---|------|--------|----------------------------------------------|---|-----|---|-------|---|---|-----|---|-----|

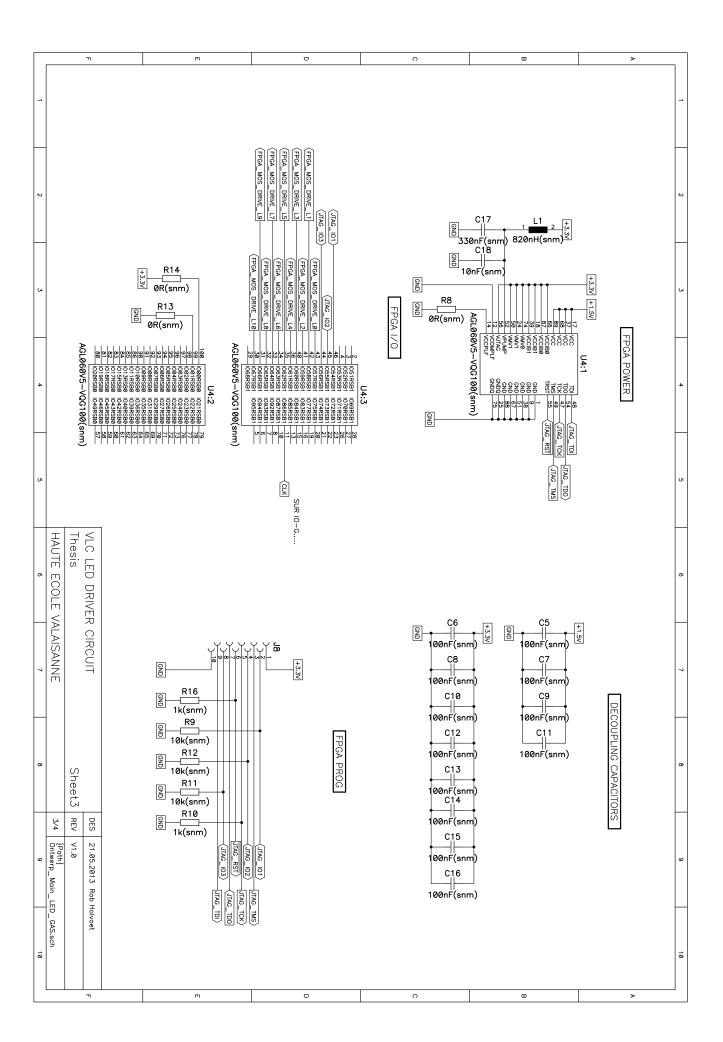

|   | H.3  | Shemat | tic 3                                        | • |     | • | <br>• | • |   |     | • | 108 |

|   |      | H.2.8  | Connection to the FPGA board                 |   |     |   |       |   |   |     |   |     |

|   |      | H.2.7  | Separation between analog and digital ground |   |     |   |       |   |   |     |   |     |

|   |      | H.2.6  | Voltage regulator                            |   |     |   |       |   |   |     |   |     |

|   |      | H.2.5  | LC filter                                    |   |     |   |       |   |   |     |   |     |

|   |      | H.2.4  | Voltage reference                            |   |     |   |       |   |   |     |   |     |

|   |      |        | Amplifier                                    |   |     |   |       |   |   |     |   |     |

|   |      | H.2.2  | High pass filter                             |   |     |   |       |   |   |     |   |     |

|   |      | H.2.1  | Ambient light rejection circuit              |   |     |   |       |   |   |     |   |     |

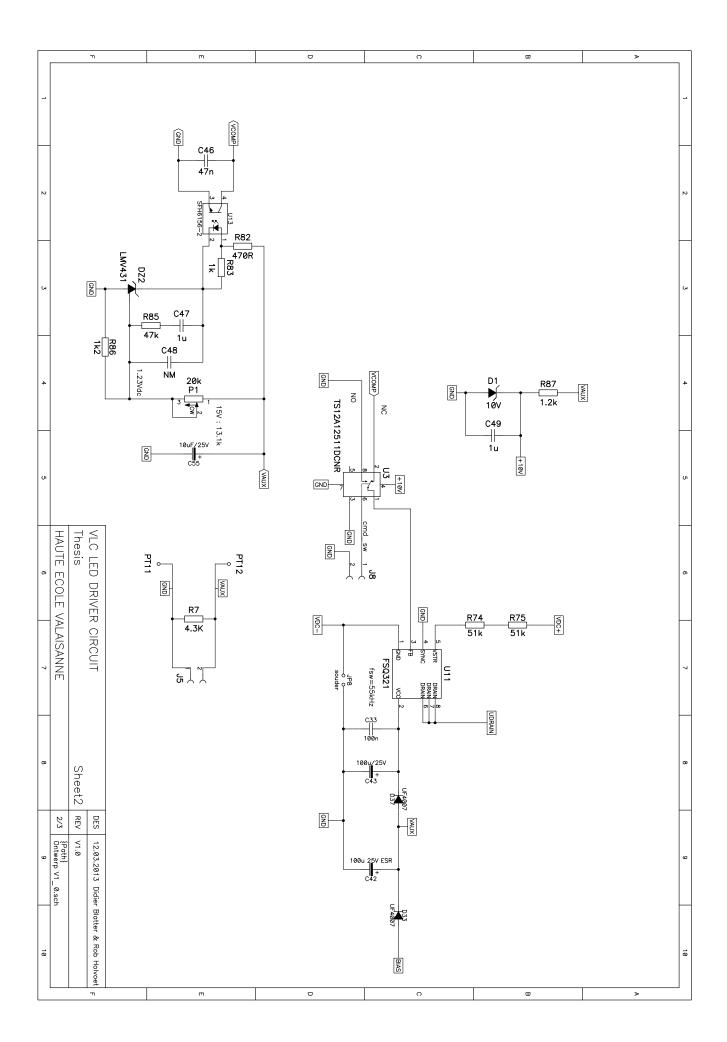

|   | H.2  |        | atic 2                                       |   |     |   |       |   |   |     |   |     |

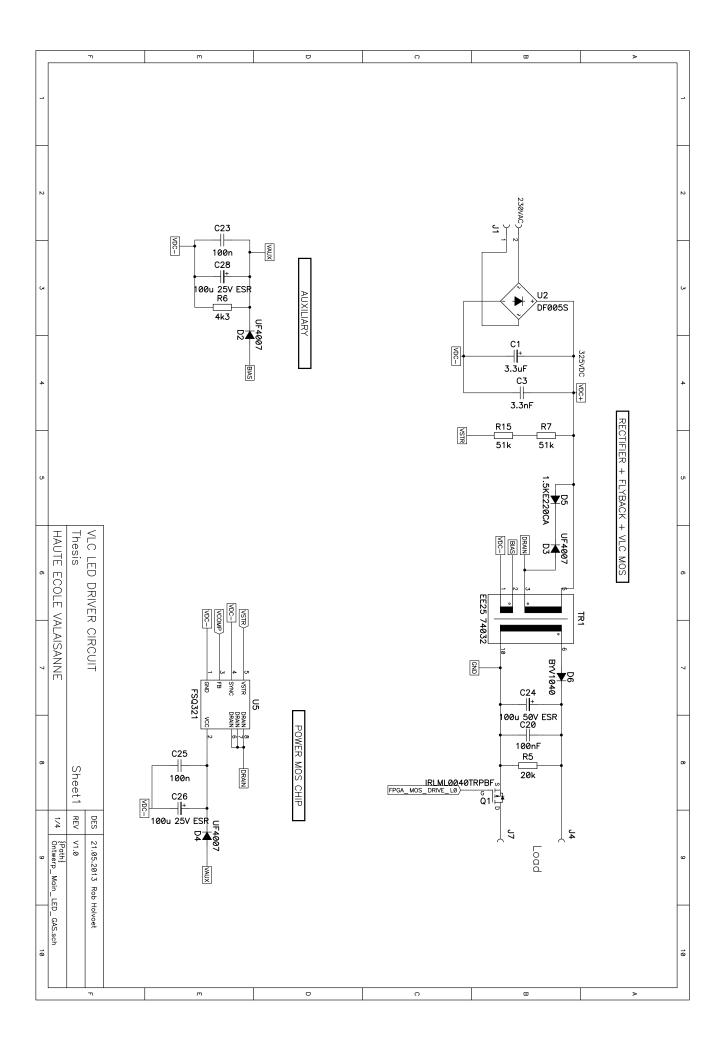

|   |      | H.1.5  | Feedback circuit                             |   |     |   |       |   |   |     |   |     |

|   |      | H.1.4  | Power switch chip and analog switch          |   |     |   |       |   |   |     |   | 99  |

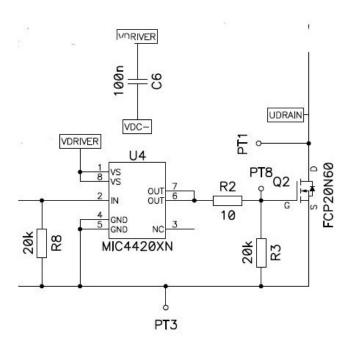

|   |      | H.1.3  | Mosfet and mosfet driver                     |   |     |   |       |   |   |     |   | 98  |

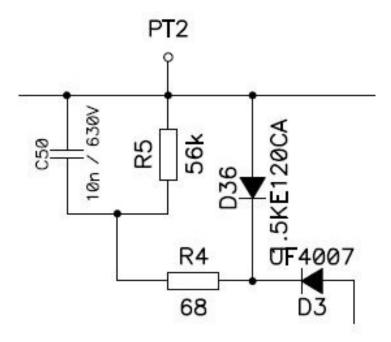

|   |      | H.1.2  | Snubber                                      |   |     |   |       |   |   |     |   | 97  |

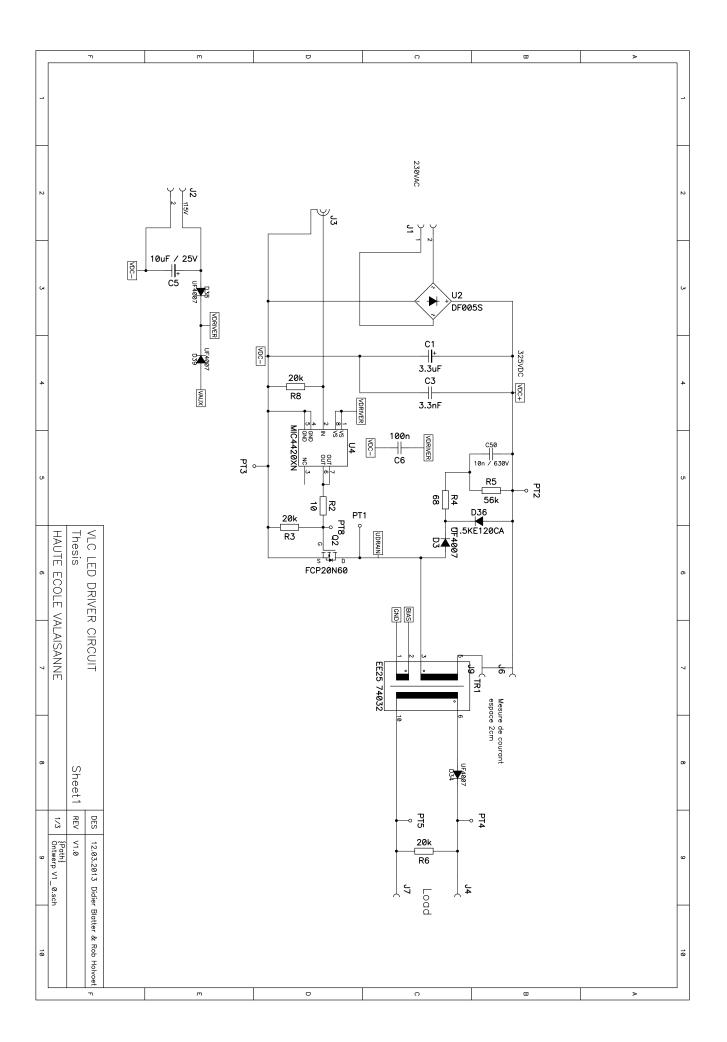

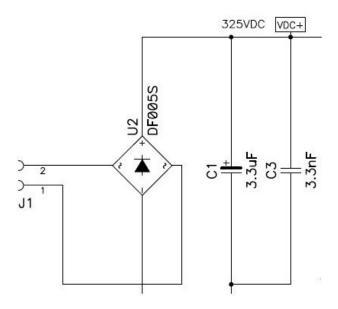

|   |      | H.1.1  | Rectifier                                    |   |     |   |       |   |   |     |   | 96  |

|   | H.1  | Shemat |                                              |   |     |   |       |   |   |     |   | 93  |

| H |      | matics |                                              |   |     |   |       |   |   |     |   | 93  |

|   |      |        |                                              | • | • • | • | <br>• | • | • | • • | • |     |

|   |      |        | sion                                         |   |     |   |       |   |   |     |   | 92  |

|   | G.3  |        | quences per bit                              |   |     |   |       |   |   |     |   | 92  |

|   | G.1  |        | quences per bit                              |   |     |   |       |   |   |     |   | 91  |

| J | G.1  |        | quence per bit                               |   |     |   |       |   |   |     |   | 90  |

| G | Data | transm | nission                                      |   |     |   |       |   |   |     |   | 90  |

|   | F.11 | Conclu | sion                                         |   |     |   |       |   |   |     |   | 89  |

|   | F.10 | n = 15 |                                              |   |     |   |       |   |   |     |   | 88  |

|   | F.9  | n = 14 |                                              |   |     |   |       |   |   |     |   | 88  |

|   | F.8  | n = 13 |                                              |   |     |   |       |   |   |     |   | 87  |

|   | F.7  | n = 12 |                                              |   |     |   |       |   |   |     |   | 87  |

|   | F.6  | n = 11 |                                              |   |     |   |       |   |   |     |   | 86  |

|   | F.5  | n = 10 |                                              |   |     |   |       |   |   |     |   | 85  |

|   | F.4  | n=9.   |                                              |   |     |   |       |   |   |     |   | 82  |

|   | F.3  | n = 8. |                                              |   |     |   |       |   |   |     |   | 81  |

|   | F.2  | n = 7. |                                              |   |     |   |       |   |   |     |   | 80  |

|   | r.1  | n = 0. |                                              | ٠ |     | • | <br>• | • |   |     | ٠ | //  |

| I.1 | VHDL   | Code                         |

|-----|--------|------------------------------|

|     | I.1.1  | ADC                          |

|     | I.1.2  | Ethernet                     |

|     | I.1.3  | Sequence generation for LEDs |

| I.2 | Python | Code                         |

|     | I.2.1  | Ethernet sender              |

|     | I.2.2  | Main script                  |

|     | I.2.3  | Functions                    |

|     | I.2.4  | Functions testing            |

|     |        |                              |

# **List of Figures**

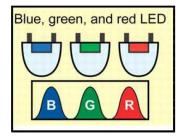

| 2.1  | Two approaches for generating white emission from LEDs.[11]               | 3  |

|------|---------------------------------------------------------------------------|----|

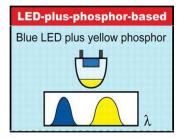

| 2.2  | Different kinds of white light.[9]                                        | 4  |

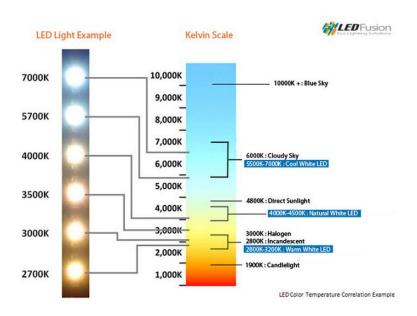

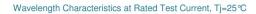

| 2.3  | Typical Color Spectrum.[3]                                                | 5  |

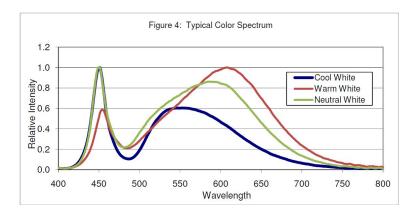

| 2.4  | Spectrum of warm-white LED in comparison with the range of the photodiode | 6  |

| 2.5  | Photodiode BPW21R                                                         | 6  |

| 2.6  | Short Circuit Current vs. Illuminance                                     | 8  |

| 2.7  | Relative Spectral Sensitivity vs. Wavelength                              | 8  |

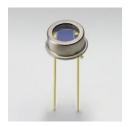

| 2.8  | Photodiode S1223                                                          | 9  |

| 2.9  | Sensitivity vs. Wavelength                                                | 10 |

| 2.10 | Model of photodiode                                                       | 10 |

| 2.11 | Main characteristics of the BXRA-30E0740-A-00 [3]                         | 11 |

| 2.12 | Other characteristics of the BXRA-30E0740-A-00 [3]                        | 11 |

| 3.1  | LED DRIVER                                                                | 12 |

| 3.2  | VLC Circuit                                                               | 13 |

| 3.3  | Flyback Converter Circuit[7]                                              | 14 |

| 3.4  | 3-bit LFSR                                                                | 15 |

| 3.5  | Block diagram 1                                                           | 17 |

| 3.6  | Block diagram 2                                                           | 18 |

| 3.7  | Result twisted pair cable (6m)                                            | 19 |

| 3.8  | Signal from on-board FPGA (yellow) and current trough LED (green)         | 20 |

| 3.9  | Block diagrams                                                            | 20 |

| 4.1  | Block diagram receiver                                                    | 21 |

| 4.2  | Step-up converter (1.2V to 3.3V)                                          | 22 |

| 4.3  | Step-up converter (1.2V to 5V)                                            | 23 |

| 4.4  | Current-voltage converter                                                 | 24 |

| 4.5  | RC high pass filter                                                       | 25 |

| 4.6  | Output receiver with RC-filter                                                                | 26 |

|------|-----------------------------------------------------------------------------------------------|----|

| 4.7  | Ambient light filter circuit with capacitor                                                   | 26 |

| 4.8  | Output receiver with condensator                                                              | 27 |

| 4.9  | Receiver circuit                                                                              | 27 |

| 4.10 | Creating a virtual ground for single supply operation                                         | 28 |

| 4.11 | LC filter with $f_{cut-off} = 500$ kHz and $Z_{in} = Z_{out} = 50 \Omega \dots \dots$         | 29 |

| 4.12 | LC filter with $f_{cut-off} = 500$ kHz and $Z_{in} = Z_{out} = 50 \Omega$ (PCB)               | 29 |

| 4.13 | Spectrum LC filter measured with network analyzer (50 $\Omega$ input and output               |    |

|      | impedance)                                                                                    | 30 |

| 4.14 | Simulation spectrum LC filter with $Z_{in} = 1 \Omega$ and $Z_{out} = 300 \Omega$             | 30 |

| 4.15 | Signal before and after filter at 2,3 m (square wave)                                         | 31 |

| 4.16 | Signal before and after filter at 2,3 m (LFSR)                                                | 31 |

| 4.17 | Simulation spectrum LC filter with $Z_{in} = 1 \Omega$ and $Z_{out} = 300 \Omega$ (redesign). | 32 |

| 4.18 | Signal before and after filter at 2,3 m (LFSR) with new LC filter                             | 32 |

| 4.19 | Timing diagram 12-bit ADC                                                                     | 33 |

| 4.20 | Signals $\overline{CS}$ and SDATA                                                             | 34 |

| 4.21 | FPGA board                                                                                    | 34 |

| 4.22 | THD (dB) vs. Source impedance ( $\Omega$ )                                                    | 35 |

| 4.23 | Input signal ADC when driven by FPGA (LFSR at 2,3m) $\dots \dots$                             | 35 |

| 4.24 | Input signal ADC when driven by FPGA measured with probe with ground                          |    |

|      | wire                                                                                          | 36 |

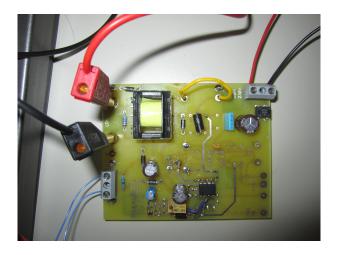

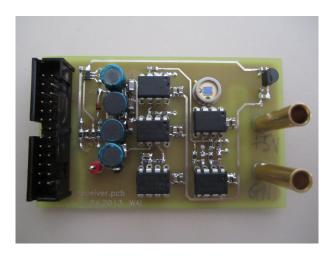

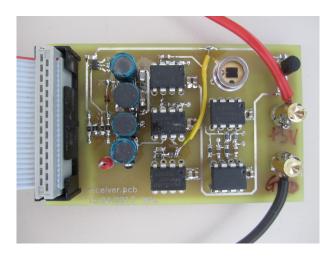

| 4.25 | PCB receiver                                                                                  | 36 |

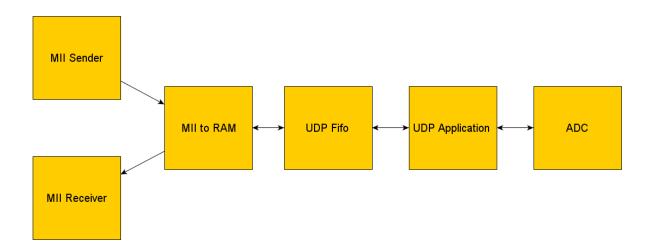

| 5.1  | Structure to send and receive packets over Ethernet                                           | 38 |

| 5.2  | Structure to write the samples in RAM and read from RAM                                       | 39 |

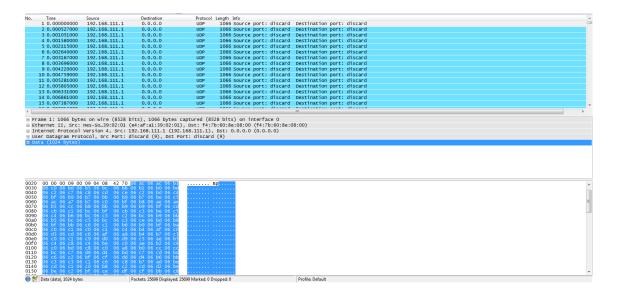

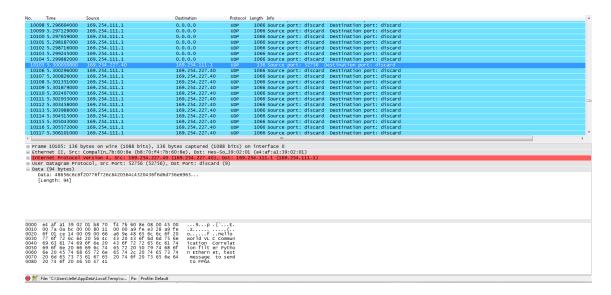

| 5.3  | Received UDP packets in Wireshark                                                             | 40 |

| 5.4  | Construction of receiver and connection to the PC                                             | 41 |

| 6.1  | Network adapters on PC                                                                        | 42 |

| 6.2  | ARP table                                                                                     | 43 |

| 6.3  | Sending a UDP packet to FPGA                                                                  | 44 |

| 6.4  | Block diagram of the main code                                                                | 44 |

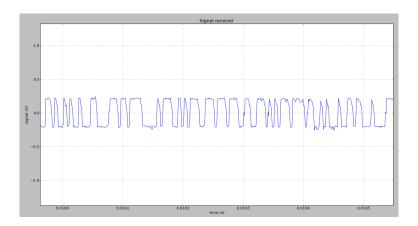

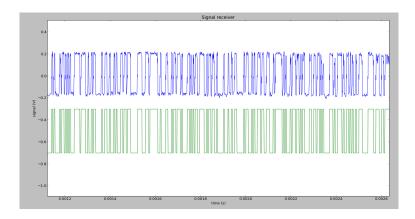

| 6.5  | Graph received samples (bit sequence of 1023 bits)                                            | 45 |

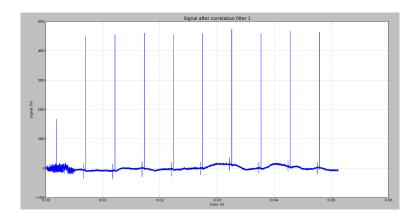

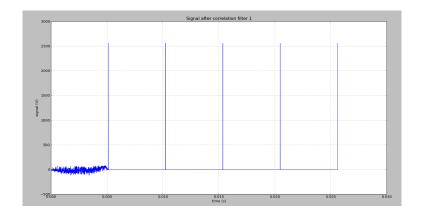

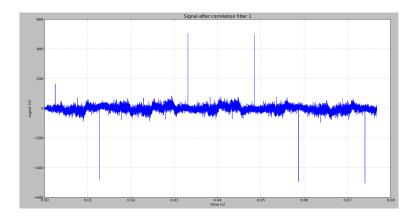

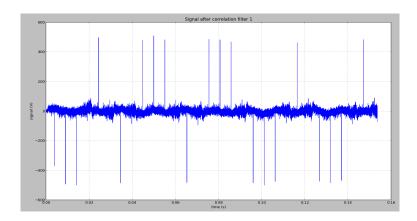

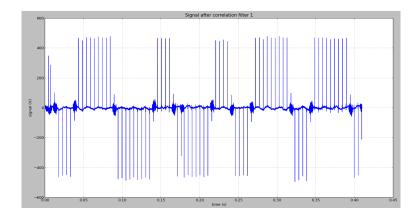

| 6.6  | Graph received samples after correlation filter (bit sequence of 1023 bits) .                 | 47 |

| 6.7  | Auto-correlation for a 10-bit sequence                                                        | 47 |

| 6.8  | Comparison between received signal and ideal signal                                           | 48 |

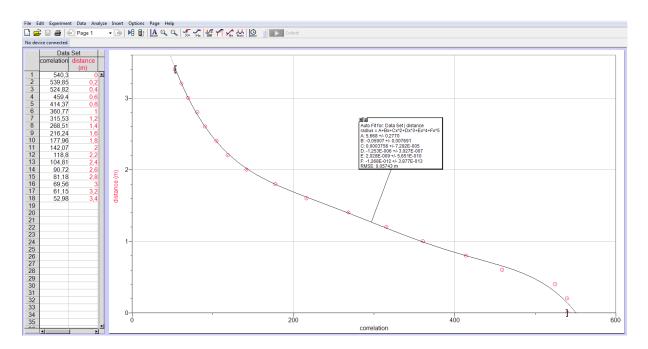

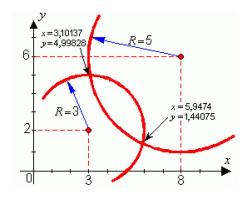

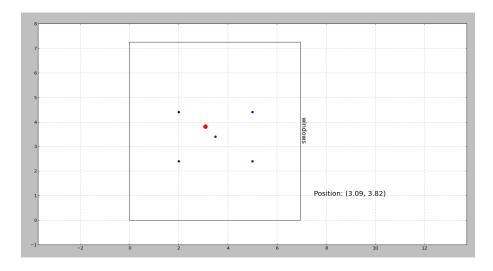

| 6.9  | Fitting correlation value vs. radius for first LED                                            | 50 |

| 6.10 | intersection points of 2 circles                                                    |

|------|-------------------------------------------------------------------------------------|

| 6.11 | Position calculation (graphical view)                                               |

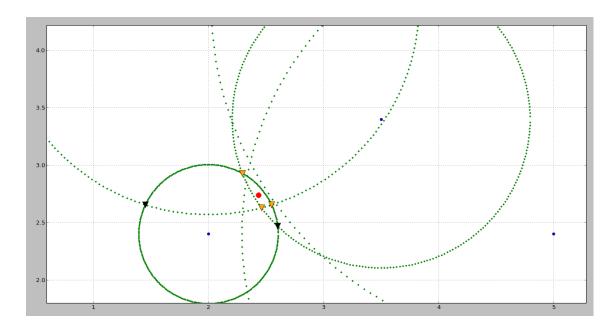

| 7.1  | Graphical view of the position of the receiver in the room                          |

| B.1  | Thermal circuit[4]                                                                  |

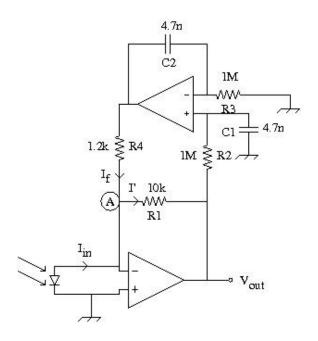

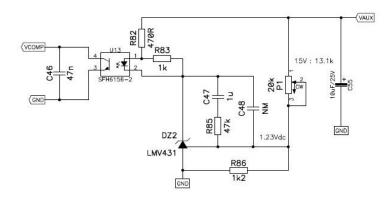

| C.1  | Ambient light rejection circuit 61                                                  |

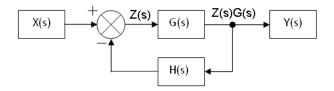

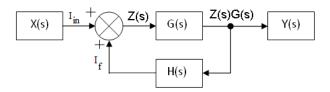

| C.2  | Closed-loop system                                                                  |

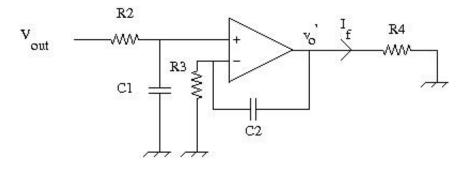

| C.3  | Feedback circuit                                                                    |

| C.4  | Closed-loop system with addition                                                    |

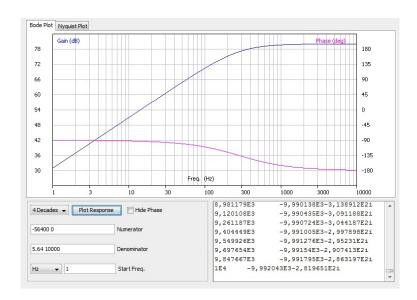

| C.5  | Bode plot $H_{tot}(s)$                                                              |

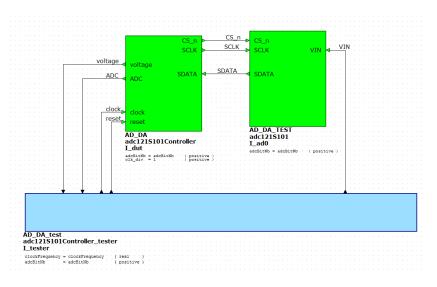

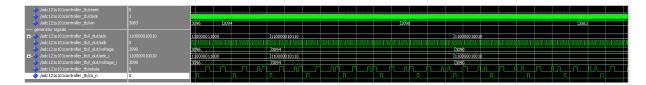

| D.1  | Testbench ADC                                                                       |

| D.2  | Simulation ADC                                                                      |

| D.3  | Testbench Ethernet                                                                  |

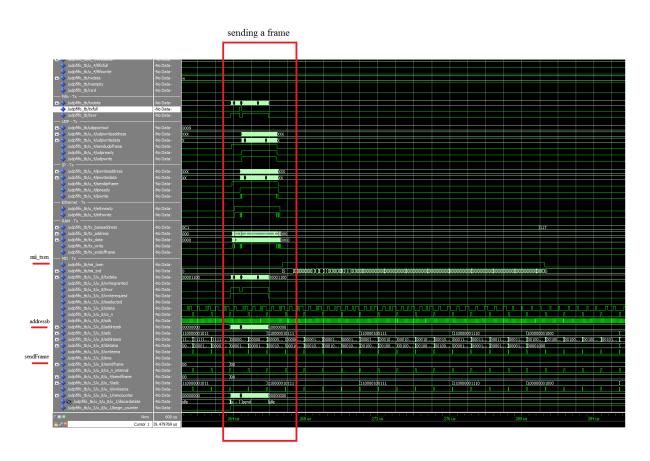

| D.4  | Simulation sending Ethernet frames                                                  |

| E.1  | Rectified voltage(Yellow) and input current(green)                                  |

| E.2  | Primary current(Yellow) and secondary current(green) 71                             |

| E.3  | Primary current(green) and rectified input voltage(Yellow)                          |

| E.4  | Primary current(Yellow) and secondary current(green) 72                             |

| E.5  | Voltage over the LED (Yellow) and current through the LED(green) 73                 |

| E.6  | Voltage over the LED (Yellow) and current through the LED(green) 73                 |

| E.7  | extra circuitry on breadboard                                                       |

| E.8  | Current through LED(Yellow) and voltage over the LED ( 17.8V to 30.7V)(green)       |

| E.9  | Current through LED(Yellow) and signal from FPGA (green)                            |

| E.10 |                                                                                     |

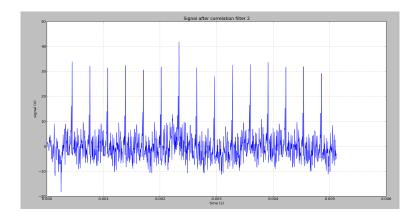

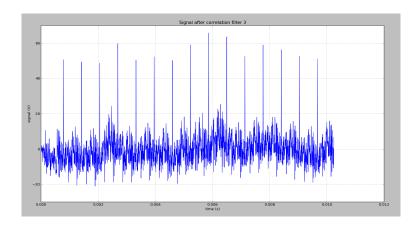

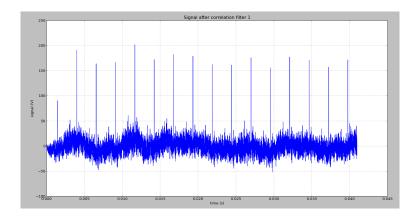

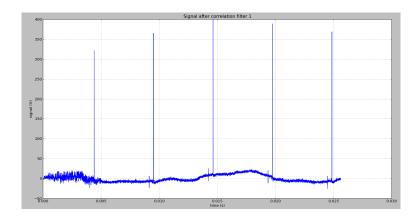

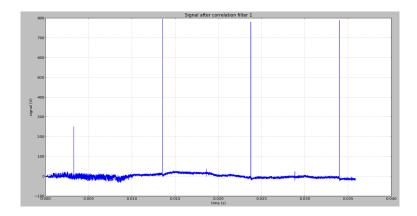

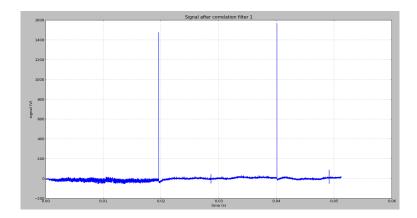

| F.1  | Graph received signal after correlation filter (6-register LFSR), one LED burning   |

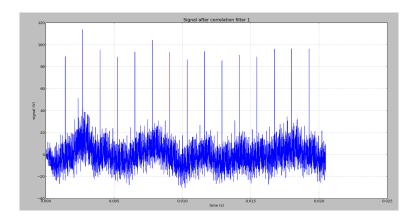

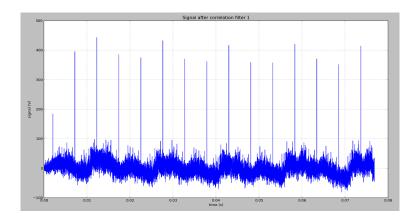

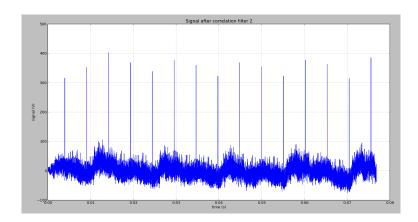

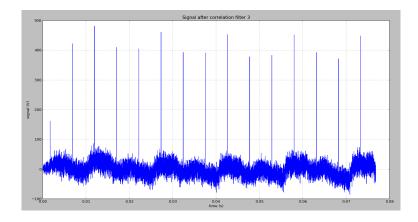

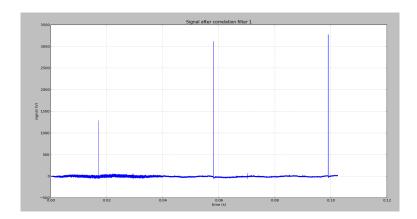

| F.2  | Graph received signal after correlation filter 1 (6-register LFSR ), 5 LEDs burning |

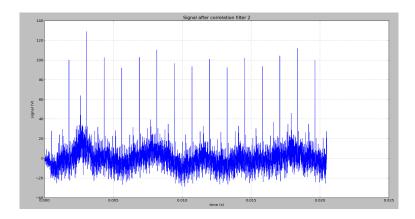

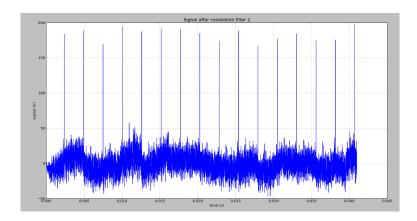

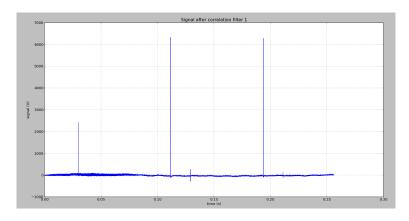

| F.3  | Graph received signal after correlation filter 2 (6-register LFSR ), 5 LEDs burning |

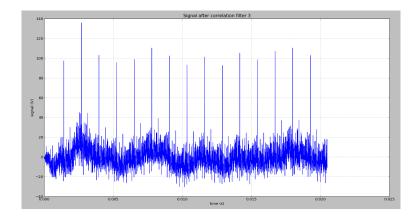

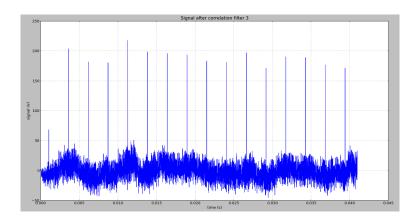

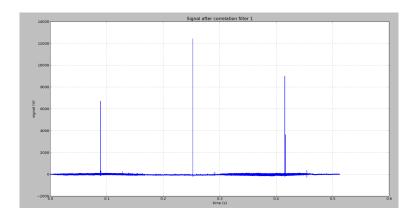

| F.4  | Graph received signal after correlation filter 3 (6-register LFSR ), 5 LEDs burning |

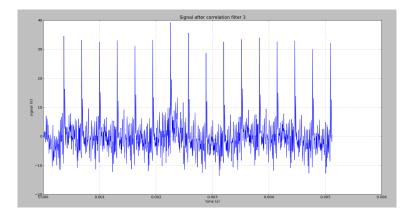

| F.5  | Graph received signal after correlation filter 1 (7-register LFSR bit LFSR), 5 LEDs burning | 80 |

|------|---------------------------------------------------------------------------------------------|----|

| F.6  | Graph received signal after correlation filter 2 (7-register LFSR ), 5 LEDs burning         | 80 |

| F.7  | Graph received signal after correlation filter 3 (7-register LFSR ), 5 LEDs burning         | 81 |

| F.8  | Graph received signal after correlation filter 1 (8-register LFSR bit LFSR), 5 LEDs burning | 81 |

| F.9  | Graph received signal after correlation filter 2 (8-register LFSR ), 5 LEDs burning         | 82 |

| F.10 | Graph received signal after correlation filter 3 (8-register LFSR ), 5 LEDs burning         | 82 |

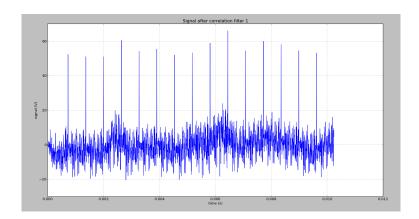

| F.11 | Graph received signal after correlation filter 1 (9-register LFSR ), 5 LEDs burning         | 83 |

| F.12 | Graph received signal after correlation filter 2 (9-register LFSR ), 5 LEDs burning         | 83 |

| F.13 | Graph received signal after correlation filter 3 (9-register LFSR ), 5 LEDs burning         | 84 |

| F.14 | Graph received signal after correlation filter (10-register LFSR ), one LED burning         | 85 |

| F.15 | Graph received signal after correlation filter 1 (10-register LFSR ), 5 LEDs burning        | 85 |

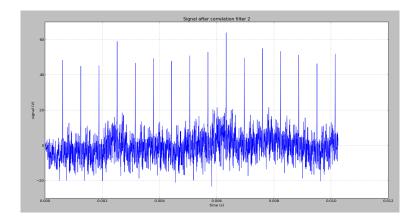

| F.16 | Graph received signal after correlation filter 2 (10-register LFSR ), 5 LEDs burning        | 86 |

| F.17 | Graph received signal after correlation filter 3 (10-register LFSR ), 5 LEDs burning        | 86 |

| F.18 | Graph received signal after correlation filter (11-register LFSR), one LED burning          | 87 |

| F.19 | Graph received signal after correlation filter (12-register LFSR), one LED                  |    |

| F.20 | burning                                                                                     | 87 |

| F.21 | burning                                                                                     | 88 |

| F.22 | burning                                                                                     | 88 |

| G 1  | Graph received signal after correlation filter (10 bit LESP), one LED                       | 89 |

| G.1  | Graph received signal after correlation filter (10-bit LFSR), one LED burning               | 91 |

| G.2  | Graph received signal after correlation litter (10-bit LFSK), 3 LEDS burning                | 91 |

| G.3  | Graph received signal after correlation filter (10-bit LFSR), one LED burning |

|------|-------------------------------------------------------------------------------|

| H.1  | PCB sender schematic 1, without unneeded parts                                |

| H.2  | Bridge rectifier and reservoir capacitors                                     |

| H.3  | Snubber                                                                       |

| H.4  | Mosfet with mosfet driver                                                     |

| H.5  | Power switch chip                                                             |

| H.6  | Feedback circuit for powerswitch                                              |

| H.7  | PCB receiver                                                                  |

| H.8  | Comparison output signal with different cut-off frequency of HPF 105          |

| H.9  | PCB receiver with some modifications                                          |

| H.10 | PCB sender schematic 2, with FPGA mounted                                     |

|      |                                                                               |

# **List of Tables**

| 2.1 | Characteristics of BPW21R photodiode                       | 6  |

|-----|------------------------------------------------------------|----|

| 2.2 | Characteristics of S1223 photodiode                        | 9  |

| 3.1 | Comparative table between different switch uses            | 17 |

| 6.1 | Measurements radius versus correlation value with each LED | 49 |

# List of symbols and acronyms

## **Symbols**

$f_{cut-off}$  Cut-off frequency

## Acronyms

| ADC         | Analog-to-digital converter      |

|-------------|----------------------------------|

| ARP         | Address Resolution Protocol      |

| ESR         | Equivalent Series Resistance     |

| FIFO        | First in, first out              |

| <b>FPGA</b> | Field-programmable gate array    |

| LED         | Light Emitting Diode             |

| LFSR        | Linear Feedback Shift Register   |

| LSB         | Least Significant Bit            |

| MII         | Media Independent Interface      |

| MSB         | Most Significant Bit             |

| RAM         | Random Accessible Memory         |

| THD         | <b>Total Harmonic Distortion</b> |

| UDP         | User Datagram Protocol           |

| VLC         | Visible Light Communication      |

| PD          | Photodiode                       |

## **Chapter 1**

## Introduction

LEDs are semiconductor devices that emit light when biased in the forward direction of the p-n junction. LEDs present many advantages over traditional light sources, including lower energy consumption, longer lifetime, improved robustness and smaller size. A significant attribute of LEDs is their ability to switch on and off thousands of times per second. No other lighting technology has this capability. This switching occurs at ultra-high speeds, so far beyond what the human eye can detect, that the light appears to be constantly on. These embedded signals are emitted from the LEDs in the form of binary code; 'off' equals zero and 'on' equals one. This is what they call visible light communication (VLC). When VLC equipment and devices are placed throughout a building of geographical area, a comprehensive wireless communication network can be created.

This thesis talks about a stand alone transmitter and a receiver that can be connected to a computer. The transmitter can be build in the ceiling and only needs 230 AC voltage to transmit digital information. The receiver will be a device to plug in a digital port of the computer. It receives information from the emitted light and send it to the PC. The transmitted information will give the receiver the possibility to determine his current position in a room by looking at the amplitude of the signals he receives from multiple LEDs. It can also be used to transmit other digital information/files.

1 Introduction 2

The structure of this report is as follows:

In chapter 2 the choice of the used LED and photodiode for the transmission is explained. Then we split the hardware research for the transmitting circuitry (chapter 3) and the receiving circuitry (chapter 4).

Chapter 3 contains information starting with some research about the chosen components and topologies. Further on it talks about the first circuitry and tests until the final board and his operation.

Chapter 4 talks about the different parts of the receiver. First, we will tell how to supply the circuit. Afterwards, we will explain the receiver circuit starting from the photodiode until the ADC used to digitalize the analog signal.

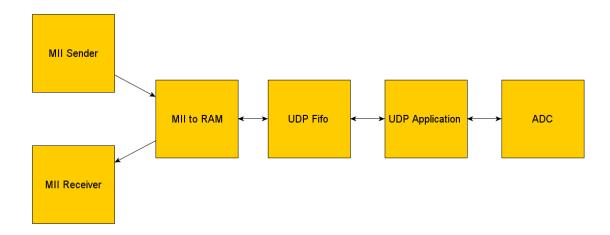

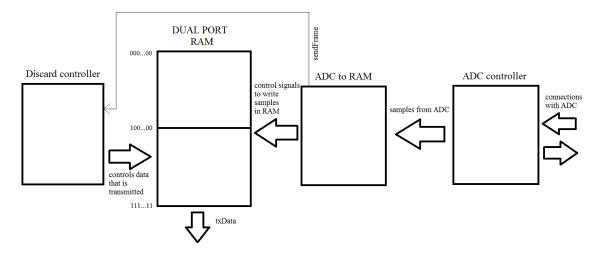

In chapter 5 we have a look how the connection with the PC is made. This contains the VHDL code used to process the data from the receiver circuitry in the FPGA and send it to the PC. At the side of the PC, we use some software to obtain that information. The processing in software is explained in chapter 6.

The final result of our thesis is presented in chapter 7. The things we couldn't do due to the time limit and the ideas we have in mind for future work are given in chapter 8.

Source code, schematics, calculations, documentation and extensive test results are found in the appendices.

## **Chapter 2**

# **Preparation and Research**

## 2.1 Choice of emitting LED and receiving photodiode

## 2.1.1 Introduction

To start this project, we first had to look for the proper LED and photodiode that we would use. We need those specifications to know what spectrum we will use to transceive, what electrical circuit we need to control the LED and to process the received data through the photodiode.

## 2.1.2 LED

As we are researching an application for indoor use and we want to use LEDs to illuminate a room and to transmit data, we will work with white light. Two approaches are generally used to generate white light with LEDs. The first approach is to combine light from, e.g.,

Figure 2.1: Two approaches for generating white emission from LEDs.[11]

red, green and blue (RGB) LEDs [11]. Typically, these triplet devices consist of a single package with three emitters and combining optics, and they are often used in application where variable color emission is required. These devices are attractive for VLC as they

offer the opportunity for transmitting different data on each LED. The other technique is to use a single blue LED which is coated with, or sometimes embedded in, a layer phosphor that emits red-shifted light upon absorbing a portion of blue light emitted by the LED. The red-shifted emission mixes additively with the nonabsorbed blue component to create the required white color (see Figure 2.1). At present, the later approach is often favored due to the lower complexity and cost. Nevertheless, in single-chip devices the phosphor typically limits the speed of overall optical response. Because our design is only a prototype and the limiting factor for data transmitting speed will be determined by the receiver circuit (limited bandwidth), we don't have to take this factor into account.

In the domain of white light you can choose 3 main types of white light LED's: Cool, Warm and Natural White LEDs (see Figure 2.2)

**Figure 2.2:** Different kinds of white light.[9]

With traditional incandescent or halogen bulbs you could not choose the colour of the light that the bulb produced as this was down to pure physics. Traditional bulbs work by passing electricity through a wire that glows hot. This glow produces the light that can be seen. Because LED bulbs are a completely different technology and much more technically advanced it is possible to choose the colour of the light that you want.

The colour temperature of light can be measured as a number on the Kelvin scale. This is represented by a number followed by the symbol 'K'. High colour temperatures of over 5000 K are said to be cool colours and often have a blue tone to them. Whereas low colour

temperatures of 2,500 - 3,200 are said to be warm colours and have yellow or orangey tones to them.[13]

In domestic lighting, 75 - 80 % of customers buy warm white LED bulbs as they offer the closest match to their old incandescent or halogen bulbs that they are replacing. The light given off by a warm white LED bulb can be described as soft and warm with a slight yellow hint to it.

Some customers purchase cool white LED bulbs if they want the brightest light possible or if they want to achieve a modern look to a room. This particularly suits colour schemes that are bright and bold and use primary colours, or even colour schemes that are predominantly white where a clean minimal look is required.

In commercial lighting the majority of customers opt for cool white bulbs. These give a brighter light but you should be careful to ensure that the colour temperature is not too high, or in practical terms the light not too cool, otherwise the effect may seem very harsh or displeasing to the eye.

These 3 main different white LEDs have a different Intensity division in the spectral band. (See Figure 2.3)

Figure 2.3: Typical Color Spectrum.[3]

## 2.1.3 Photodiode

The first part of a VLC receiver, is a photosensitive element. Mostly, a photodiode is used at the input of the receiver. The current through the photodiode, is proportional to the light falling on it. The more light it receives, the larger the current will be.

The photodiode has to operate in the same spectrum as the LED. We tested two photodiodes:

the BPW21R photodiode from Vishay and the S1223 photodiode from Hamamatsu. We will discuss both diodes and give the most important characteristics.

• In figure 6.8, you can see the spectrum of the chosen warm-white LED in comparison with the range of the BPW21R photodiode [12] (see figure 2.5). As you can see, the photodiode is sensitive in the wavelength spectrum of the LED.

Figure 2.4: Spectrum of warm-white LED in comparison with the range of the photodiode

Figure 2.5: Photodiode BPW21R

Hereby, We summarized the most important characteristics of the photodiode BPW21R in table 2.1:

Table 2.1: Characteristics of BPW21R photodiode

| Parameter                       | Value      | Unit            |

|---------------------------------|------------|-----------------|

| Sensitive area                  | 7.5        | mm <sup>2</sup> |

| Short circuit current at 1 klux | 9          | μΑ              |

| Sensitivity                     | 9          | nA<br>lux       |

| Wavelength of peak sensitivity  | 565        | nm              |

| Range of spectral bandwidth     | 420 to 675 | nm              |

| Viewing angle                   | ± 50       | 0               |

| Rise time                       | 3.1        | μs              |

| Fall time                       | 3.0        | μs              |

| Diode capacitance if $V_R=0$ V  | 1.2        | nF              |

The photodiode has a large sensitive area, what is interesting to capture enough light from the LED. The current will increase pretty fast when more light is falling on the diode because of its high sensitivity. The highest sensitivity takes place on a wavelength of 565 nm, which is in the spectrum of the LED. The rise time and fall time of a photodiode is defined as the time for the signal to rise or fall from 10% to 90% or 90% to 10% of the final value respectively. The bandwidth of the photodiode can be estimated using the formula:

$$BW pprox rac{0.35}{t_{rise}} pprox rac{0.35}{3.1 \, \mu s} pprox 112.9 \ kHz$$

The BPW21R has also a wide viewing angle, so it can pick up light from several directions. The capacitance of the diode can play an important role at higher frequencies.

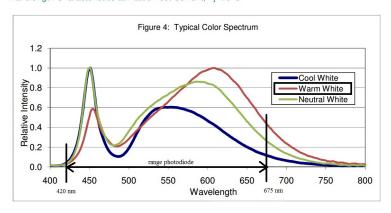

In the figure below, you can see the graph of the short circuit current in function of the illuminance. As expected from a photodiode, the current is proportional to the incident light. An interesting thing to see, is that the photodiode has to be in short circuit for linear working.

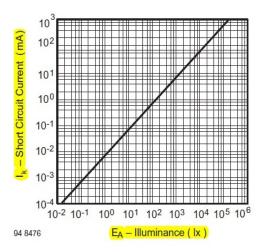

The relative spectral sensitivity versus the wavelength is shown in figure 2.7. We see that the range of spectral bandwidth (where  $S(\lambda)_{rel} = 0.5$ ) goes from 420 nm to 675 nm, as already mentioned in the characteristics. They also show the spectral response of the human eye  $V_{\lambda}Eye$ . The human eye is also a photosensitive element. It is most sensitive at a wavelength of 560 nm. The BPW21R photodiode gives thus an approximation to the spectral response of the human eye.

Figure 2.6: Short Circuit Current vs. Illuminance

Figure 2.7: Relative Spectral Sensitivity vs. Wavelength

• The BPW21R photodiode is a good choice as a receiver for the visible light communication, but can give some problems at higher frequencies because of the limited bandwidth and the capacitance. So, we also searched for another photodiode to encounter these problems. We found the S1223 photodiode from Hamamatsu [6] (see figure 2.8).

We summarized the most important characteristics of the S1223 photodiode in

Figure 2.8: Photodiode S1223

table 2.2:

Table 2.2: Characteristics of S1223 photodiode

| Parameter                         | Value       | Unit            |

|-----------------------------------|-------------|-----------------|

| Sensitive area                    | 6.6         | mm <sup>2</sup> |

| Short circuit current at 100 lux  | 6.3         | μΑ              |

| Sensitivity at 660 nm             | 0.45        | $\frac{A}{W}$   |

| Wavelength of peak sensitivity    | 960         | nm              |

| Range of spectral bandwidth       | 320 to 1100 | nm              |

| Bandwidth                         | 30          | MHz             |

| Diode capacitance if $V_R = 20 V$ | 10          | pF              |

If we compare these characteristics with the characteristics of the other photodiode, we can notice some things:

The range of spectral bandwidth is larger. The photodiode is also sensitive in the infrared region. The diode is most sensitive in this region, but he is also sensitive in the spectrum of the LED. So, we can also use this photodiode as a receiver because we will filter the ambient light. This photodiode is more appropriate at higher frequencies because of the higher bandwidth and the smaller capacitance. The rise time can now be estimated using the formula:

$$t_{rise} \approx \frac{0.35}{BW} \approx \frac{0.35}{30 \, MHz} \approx 11.667 \; ns$$

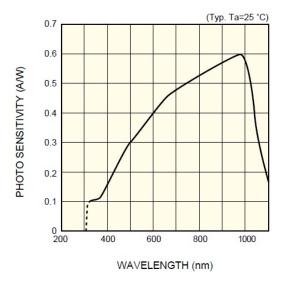

In figure 2.9, you can see the spectral response of the photodiode.

As already mentioned, the diode is most sensitive in the infrared region.

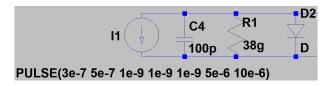

If we want to simulate a circuit with a photodiode in LT Spice, a photodiode is not available in the component library. So, we will use an equivalent model that represents the photodiode. First, we used a normal diode in parallel with a current

Figure 2.9: Sensitivity vs. Wavelength

source to model the photoelectric effect. The more light falling on the photodiode, the more current will flow through it. However, the results from the simulations and the measurements were not very similar. Then we modified the model by placing a capacitor in parallel with the diode and the current source. The capacitor represents the photodiode capacitance. You can find this value in the datasheet. Now the results were much better. Simulations and measurements were very similar. Eventually we can also add the dark resistance of the diode. But this is usually very high ( $\approx 30~$  G\Omega), so this is not very necessary. Finally we used the model below in LT Spice to represent the photodiode.

Figure 2.10: Model of photodiode

## 2.1.4 Conclusion

Because of the lowcost, the lower complexity and since we will transmit data over the whole visible spectrum, we chose the blue led with yellow phosphor coating approach. Whereas we want to implement our application in daily life, we chose to work with warm

light. The warm light has the closest match to the old incandescent of halogen bulbs that they are replacing and it has more intensity around 565 nm. After a chat with Frederic Truffer who works in the light department of the HES-SO in Sion we decided to use the BXRA-30E0740-A-00 star array led. This BXRA reaches a Typical Pulsed Flux of 860 lm. This should be enough to be detect by the photodiode at a distance of several metres. The characteristics of the chosen LED are listed in figures 2.11 and 2.12.

We chose to work with the S1223 photodiode because of the high bandwidth and the small capacitance. We will transmit data at  $200 \, \frac{\text{kbits}}{\text{second}}$ , so that the photodiode has enough time to respond to the incoming light. Because of the high sensitivity and the large sensitive area, the distance between the LED and the photodiode should be no problem. The photodiode has a sensitive range that lies in the wavelength spectrum of the LED. If we consider this, the S1223 photodiode should be an appropriate photodiode for the visible light communication.

| Values for test with testcurrent 350 mA |         |  |  |

|-----------------------------------------|---------|--|--|

| Typical Pulsed Flux<br>Tj 25°C          | 860 lm  |  |  |

| Typical DC Flux<br>Tcase 70ºC           | 770 lm  |  |  |

| Vf (Typ)                                | 28,1 V  |  |  |

| Power (Typ)                             | 9,8 W   |  |  |

| Efficacy<br>(Typ at Tj 25°C)            | 88 lm/W |  |  |

Figure 2.11: Main characteristics of the BXRA-30E0740-A-00 [3]

| Characteristics           | Minimum | Typical | Maximum | Unit    |

|---------------------------|---------|---------|---------|---------|

| Color Temperature         | 2870    | 3045    | 3220    | K       |

| Viewing angle             |         | 120     |         | Degrees |

| Typical Center Beam       |         | 260     |         | cd      |

| Candle Power              |         | 200     |         | cu      |

| Forward Voltage at test c | 25,3    | 28,1    | 30,9    | ٧       |

| DC Forward Current        |         |         | 500     | mA      |

| Peak Pulsed Current       |         |         | 700     | mA      |

| Reverse Voltage           |         |         | -45     | ٧       |

Figure 2.12: Other characteristics of the BXRA-30E0740-A-00 [3]

## **Chapter 3**

## **LED** driver circuit

## 3.1 Introduction

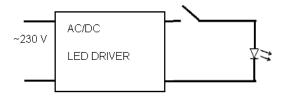

To power the LED with the mains we first need to convert the 230  $V_{AC}$  to a DC voltage and control the current through the LED. On the market you can buy a readily available LED driver, for our led we could use the 3-Watt MagTech LED Driver L03U-350 (see Figure 3.1).

#### 3-Watt MagTech LED Driver Features:

- 100 ~ 277VAC Input

- 4 ~ 12VDC Output

- · 350mA Output Current

- 1 ~ 3 Watts Output Power

- 1.57"L x 1.57"W x 0.87"H

- · UL and CE Certified

- · Short Circuit & Overload Protection

Figure 3.1: LED DRIVER

We could use this driver or make our own driver and use this together with a switch for our VLC application (see Figure 3.2).

Most drivers use Switch Mode Power Supply (SMPS) topologies where the output voltage or current is determined by the frequency at what a switch is turned on and off. We wonder if it is possible to use this switch instead of an extra switch after the AC/DC converter to send information in a VLC application and control the output current at the same time. So we will construct our own LED driver and control the current through the LED. At first we will investigate the possibilities of sending data by controlling the switch of a Switch Mode Power Supply with an FPGA. The use of a switch after the LED driver will also be

Figure 3.2: VLC Circuit

investigated.

## 3.2 Power Supply Topologies

There are a lot of Power Supply Topologies we could use for our application. We must use an Switch Mode Power Supply as we want to control the switch for sending our data. In general this method is more interesting in comparison with series-controlled regulators that don't use a switch, looking at the power loss. A list with a short description of these SMPS topologies is given in appendix A.

We will use the flyback converter due to his low cost, simplicity of design, small size and intrinsic efficiency. Other advantages of the flyback transformer over circuits with similar topology include isolation between primary and secondary and the ability to provide multiple outputs.

## 3.3 Flyback Converter

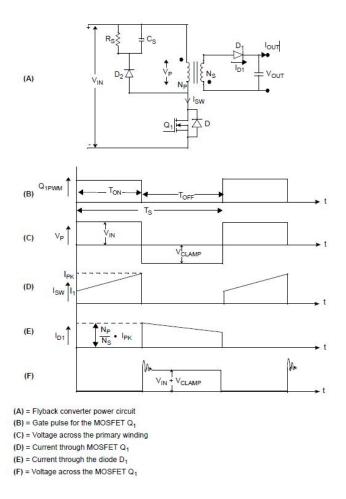

A flyback converter is a transformer-isolated converter based on the basic buck boost topology. The basic schematic and switching waveforms are shown in Figure 3.3. In a flyback converter, a switch  $(Q_1)$  is connected in series with the transformer  $(T_1)$  primary. The transformer is used to store the energy during the ON period of the switch, and provides isolation between the input voltage source  $V_{IN}$  and the output voltage  $V_{OUT}$ . In a steady state of operation, when the switch is ON for a period of  $T_{ON}$ , the dot end of the winding becomes positive with respect to the non-dot end. During the  $T_{ON}$  period, the diode  $D_1$  becomes reverse-biased and the transformer behaves as an inductor. The value of this inductor is equal to the transformer primary magnetizing inductance  $L_M$ , and the stored magnetizing

energy from the input voltage source  $V_{IN}.E_p = \frac{1}{2} \cdot I_{PK}^2 \cdot L_M \& I_{PK} = \frac{V_{IN} \cdot T_{ON}}{L_M}$ Therefore, the current in the primary transformer (magnetizing current  $I_M$ ) rises linearly

Therefore, the current in the primary transformer (magnetizing current  $I_M$ ) rises linearly from its initial value  $I_1$  to  $I_{PK}$ , as shown in 3.3(D). As the diode  $D_1$  becomes reverse-biased, the load current ( $I_{OUT}$ ) is supplied from the output capacitor ( $C_O$ ). The output capacitor

**Figure 3.3:** Flyback Converter Circuit[7]

value should be large enough to supply the load current for the time period  $T_{ON}$ , with the maximum specified drop in the output voltage. At the end of the  $T_{ON}$  period, when the switch is turned OFF, the transformer magnetizing current continues to flow in the same direction. The magnetizing current induces negative voltage in the dot end of the transformer winding with respect to non-dot end. The diode  $D_1$  becomes forward-biased and clamps the transformer secondary voltage equal to the output voltage. The energy stored in the primary of the flyback transformer transfers to secondary through the flyback action. This stored energy provides energy to the load, and charges the output capacitor. Since the magnetizing current in the transformer cannot change instantaneously at the instant the switch is turned OFF, the primary current transfers to the secondary, and the amplitude of the secondary current will be the product of the primary current and the transformer turns ratio,  $N_P/N_S$ .

## **3.4** LFSR

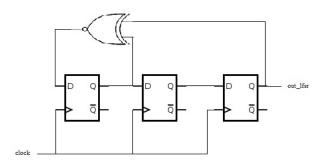

To control the mosfet for sending signals with the LED we need a certain signal to be generated. We chose to use a semi-random generated signal. For this we use a shift register expanded with xor functions (this is an example of an LFSR).

#### 3.4.1 First tests

For the first tests we chose to work with a 3-bit LFSR (figure 3.4). This LFSR generates a bit sequence of 0,0,1,0,1,1,0.

Figure 3.4: 3-bit LFSR

We can program this LFSR in an FPGA. We used an FPGA board available at school with a Spartan XC3S500E FPGA from Xilinx on it to do the testing.

#### 3.4.2 Final LFSR

As will be explained in the further text, we will only need a semi-random LFSR to be generated by a FPGA we will mount on the board. To be able to detect these LFSRs, we will use correlation. Later on we will test the response for LFSRs with different lengths. We always use maximum feedback xor combinations to generate a binary sequence with a length of  $2^{m-1}$  bits, where m is the length of the used register. [8]<sup>1</sup>

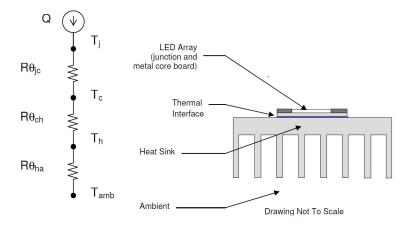

## 3.5 LED Heatsink

When a voltage is applied across the junction of an LED, current flows through the junction generating light. It is a common misconception that LEDs don't generate heat. While

<sup>&</sup>lt;sup>1</sup>a list of tabs for maximal feedback can be found on http://www.newwaveinstruments.com/resources/articles/m\_sequence\_linear\_feedback\_shift\_register\_lfsr.htm

essentially no heat is generated in the light beam (unlike conventional light sources), heat is generated at the junction of the LED Array and must be effectively managed. As LEDs are not 100 % efficient at converting input power to light, some of the energy is converted into heat and must be transferred to the ambient. The amount of heat generated from the LED Array that must be transferred to the ambient may be conservatively estimated to be 85 % of the power that is applied to the LED Array and is calculated as in Equation 3.1

$$P_d = V_f \cdot I_f \cdot 0.854 \tag{3.1}$$

Where:

$P_d$  is the thermal power to be dissipated

$V_f$  is the forward voltage of the device

$I_f$  is the current flowing through the device

The power calculation should be made for maximum dissipated power, which is computed using the Maximum  $V_f$  at the drive current desired.

Heat generated at the LED junction must be transferred to the ambient via all elements that make up the thermal management solution. These elements include the LED Array, the thermal interface material used between the LED Array and heat sink, the heat sink, the luminaire enclosure (if applicable), and other components that come in contact with the lighting assembly. These elements transfer heat to the ambient. We will use a heat sink to manage the temperature at the case of the LED array. The calculation of the maximum needed thermal resistance of the heat sink is included in appendix B.

We chose to use the SA-LED-151E - HEATSINK, LED, 50.8MM of OHMIT which have a thermal resistance of  $3.2^{\circ}C/W$ , which is way below the maximum of  $11.85^{\circ}C/W$ . This heat sink should keep the LED junction on a temperature below  $70.5^{\circ}C$  and the casing on a temperature below  $57.01^{\circ}C$ .

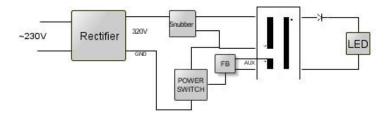

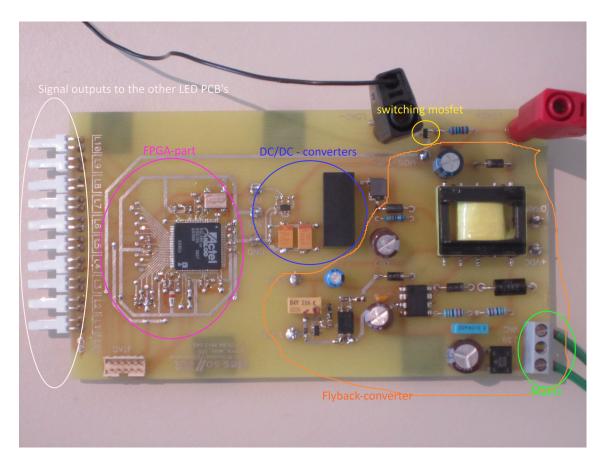

## 3.6 Testing circuit 1

For the first tests, we designed a transformer circuit (schematic included in annex H.1) where we implement a power switch chip for the start up cycle and also to do the first tests. With a switch we can turn of the function of the POWER switch and give the control of the flyback to the FPGA. For the feedback of the power switch we use an analog feedback circuit, for the feedback to the FPGA we can expand our PCB with a ADC to measure the current through the LED. By reading this current, the FPGA will interact by changing the duty cycle of the control signal for the transformer switch when needed.

#### **3.6.1** Tests

#### First test

For the first test, we only looked at the functionality of the transformer operating with the power switch chip. The block diagram is given in fig 3.5. The results are discussed in appendix E.1.

Figure 3.5: Block diagram 1

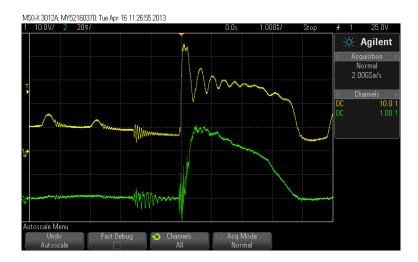

As seen in appendix E.1, a custom made transformer should be calculated to have a maximum efficiency and maximum luminance. Due to the restriction of time and great advantages (shown in table 3.1) of the topology when placing a switch in serie with a LED driver (see following sections) we will continue by using the topology where we place a switch after the flyback.

| Property               | using switch of flyback            | using switch in series with LED |

|------------------------|------------------------------------|---------------------------------|

| Transformer            | custom made                        | general transformer can be used |

|                        |                                    | with tolerance in values        |

| Design                 | multiple feedbackloops needed,     | relatively simple design        |

|                        | change of flyback switch after     |                                 |

|                        | startup, larger circuitry and more |                                 |

|                        | components                         |                                 |

| Transmission frequency | fixed and determined by            | can be chosen by the user       |

|                        | transformer                        |                                 |

**Table 3.1:** Comparative table between different switch uses

#### **Second test**

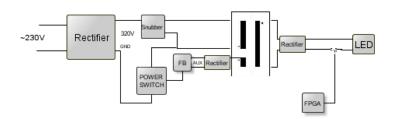

We choose to obtain the same circuitry, only using the power switch chip and placing a capacitor in parallel with the LED as load storage. A switch will be used to generate current pulses trough the LED. For this tests we use a external programmed FPGA (We place it on

the same ground of our circuitry) to control the switch. This is shown in block diagram 3.6. The results are shown in appendix E.5.

Figure 3.6: Block diagram 2

As the results of the second test met our expectations, we designed a new circuitry that will be discussed in the next paragraph.

## 3.7 Testing circuit 2

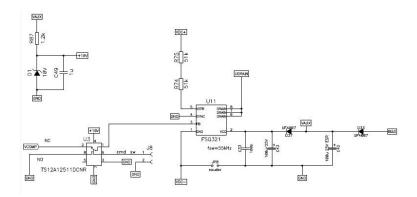

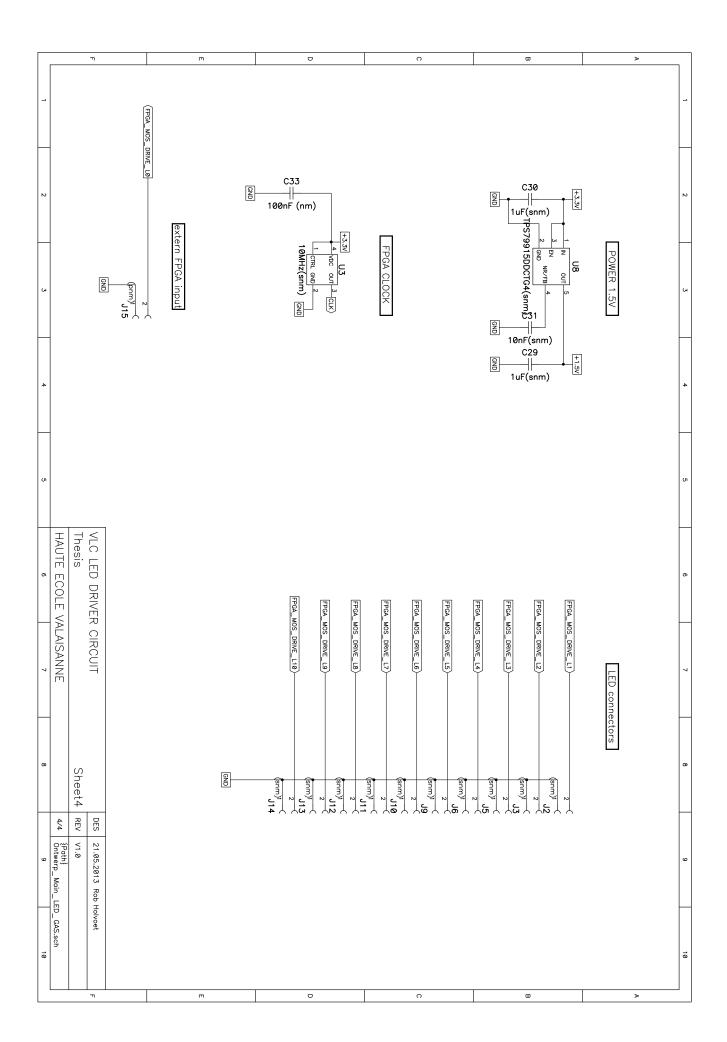

For the new circuit, we will mount an FPGA on the board. We will use one FPGA to generate the binary sequences for all the different LEDs to obtain a lower cost and a synchronization of the different LEDs. We expect that the synchronisation of the LEDs will make it easier to distinguish the different bit sequences in the received signal. We used the Actel igloo AGL 060V5 -VOG100. Because of his PROM memory we don't have to program it every time we power it. The Actel igloo don't support complicated designs, what we don't need as we just want to generate LFSRs. This FPGA was used in a previous project at HES-SO Valais/Wallis what makes it easier to implement it in our design. We used that previous design as a template for our application. We used only a part of testing circuit 1 and added the FPGA, a DC/DC converter(to power the FPGA), a mosfet (as switch in serie with the LED) and an extra storage capacitor for a normal working of the Flyback. The schematic is added in appendix H.3. We use one schematic for the PCBs with and without FPGA. All the components with \*(snm) don't have to be mounted on the PCBs without FPGA. The VHDL code and block diagrams used to program the FPGA can be found in section 3.7.3.

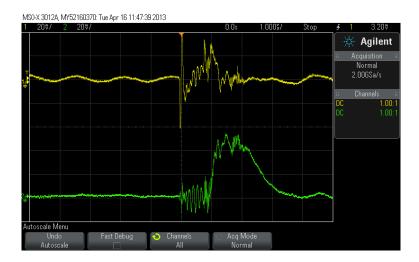

## 3.7.1 Twisted pair cable

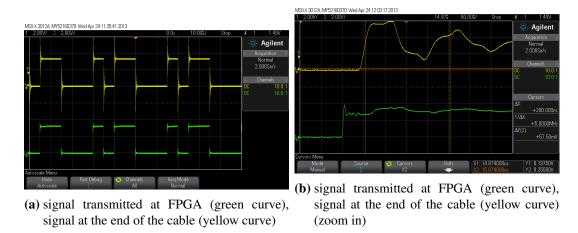

To drive the MOSFETs of the different LED circuits, we need to transport a blockwave on different places in the room. To transport these signals we have to look how we can transport them without great distortion or noise. The simplest way to do this is to send through a twisted pair cable. We test the deformation of the signal on a twisted pair cable of 6 meter (largest distance of 2 LEDs in a room). The result is given in figure 3.7. We see a

ringing effect et the end of the cable. As this ringing only lasts for about 300 ns and our bit period is 5  $\mu$ s, this signal is only used as switch and we already have noise and peaks in our transmitted light signal (which are not detected by the receiver). This result is sufficient. We will connect the output of the FPGA directly with the mosfets in series with the LED. If we would work on a higher frequency, we would have to take this ringing into account.

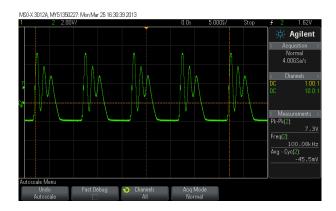

**Figure 3.7:** Result twisted pair cable (6m)

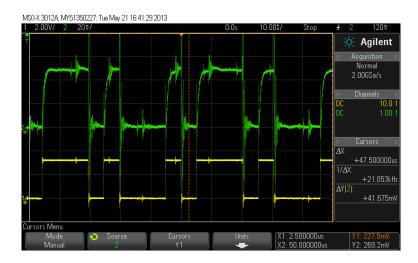

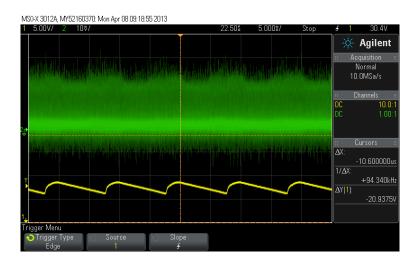

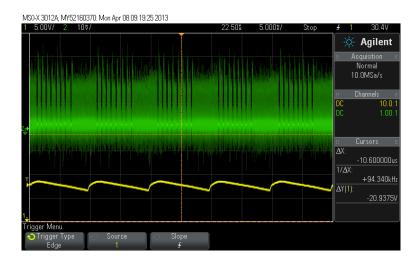

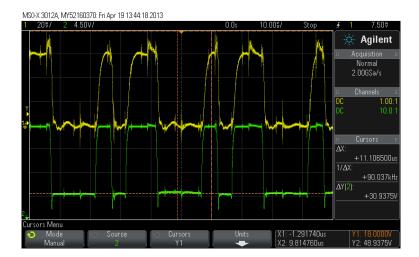

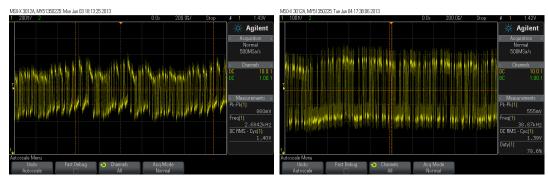

#### **3.7.2** Tests

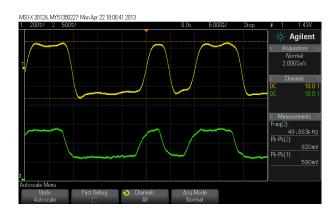

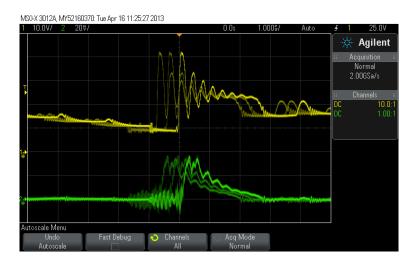

We regulate the potentiometer to get a current of maximum 500 mA through the LED and program the FPGA to generate LFSRs. In figure 3.8 you can see the current trough the LED in comparison with the signal sent by the FPGA. We can see that we have some ripple and spikes on the current signal. We won't try to prevent this because this has no effect on the received signal by the receiver circuit. To regulate the LEDs on the same intensity we can look on the oscilloscope with a current probe. But we will check on every board by looking at  $V_{AUX}$  (here 16.5 V). We checked and tested the resistance of the potentiometer and it was each time around 15 k $\Omega$ .

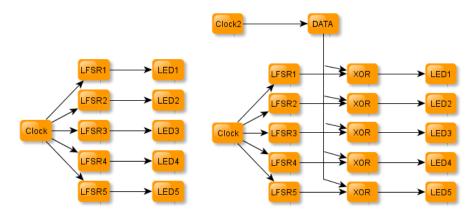

#### 3.7.3 VHDL of sender FPGA

As already mentioned we generate sequences with a FPGA. For each led we need a different LFSR (3.9a). The MSB of the LFSR is sent to the mosfet of each LED which get in conduction (1) or isolation(0) mode. When the MOSFET is in conduction mode, current flows through the LED and the LED emits light. When the MOSFET is in isolation mode, no current can go through the LED so the LED is not illuminating. For the readability of the code we wrote all the LFSRs in one block and used this for every LED. The correct LFSR is chosen by the number of the LED the block gets as a generic. The code can be found in appendix I.1.3.

Figure 3.8: Signal from on-board FPGA (yellow) and current trough LED (green)

We also did some tests in appendix G to send data over these LFSRs by just inverting the sequences. The block diagram is shown in figure 3.9b. The second clock represent a clock with a frequency of  $\frac{f_{clock}}{2^{n-1}*m}$  where n is the length of the register of the LFSR and m is a natural value. We did the tests by shifting a sequence and 'xor'ed this with the output we already had. The code is not included in this report because of its simplicity.

(a) LFSR sending sequence (b) LFSR sending sequences generation with data. generation

Figure 3.9: Block diagrams

# **Chapter 4**

# The receiver circuit

### 4.1 Introduction

We already discussed the photodiode we will use for the visible light communication. As mentioned before, the short-circuit current through the photodiode is proportional to the incident light. If we want to know the bits that are transmitted, we have to use several blocks. First of all, we will use a current-voltage converter, so that the voltage is also proportional to the incoming light. We also need a high pass filter to filter out the ambient light and the 100 Hz frequency components coming from the lighting in the building. Since the signal we will receive is weak, we will have to use an amplifier. Then, we also need an ADC to digitalize the received signal. Before the ADC, an anti-aliasing filter is needed. Finally, the digital samples have to be transmitted to a PC so we can use software to make some calculations and to find the position. We will use an Ethernet cable for the connection.

The block diagram of the receiver circuit is shown below. We will discuss the several blocks and the power supply as well in this chapter. The Ethernet connection and the data processing on the PC will each be discussed in a separate chapter.

Figure 4.1: Block diagram receiver

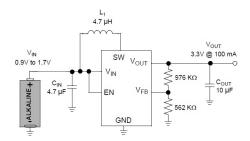

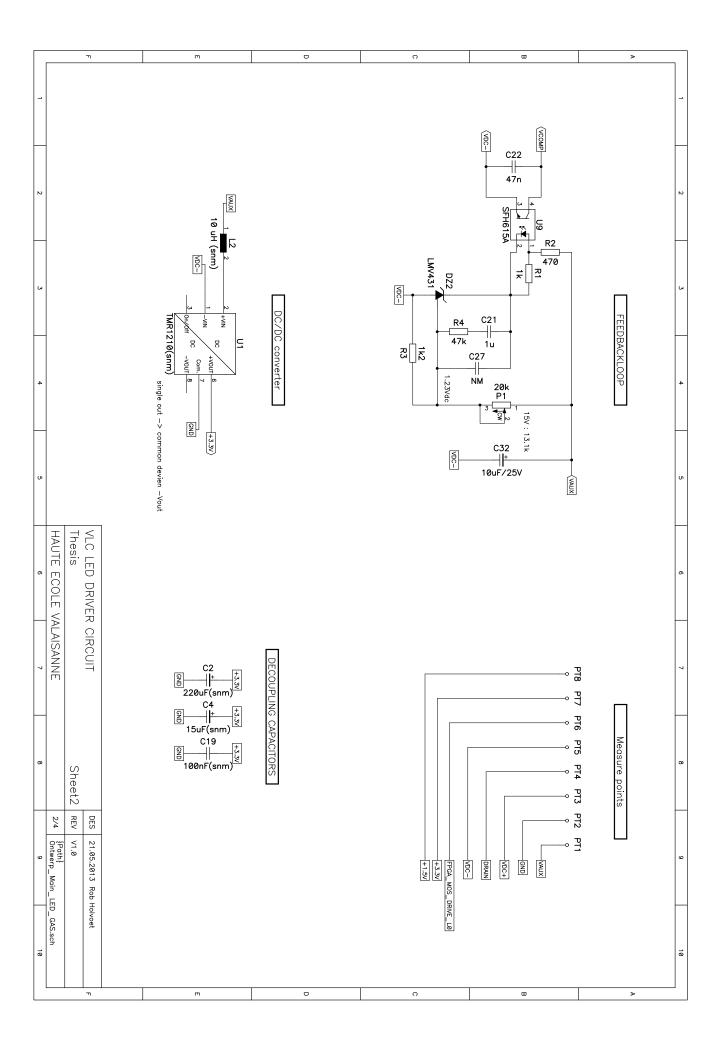

### 4.2 Power supply

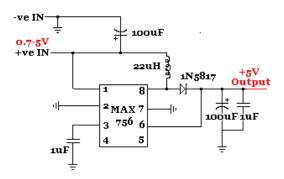

Since we want to make a handheld device, a possibility to supply the circuit is a battery. A normal battery delivers a voltage of 1.2 V or 1.5 V, what is not enough for the power supply. We can use a step-up converter (boost converter) to obtain a larger voltage. There are several good chips you can use for this purpose. We found a circuit to boost the 1.2 V to 3.3 V in the datasheet of the *MCP 1640* of Microchip <sup>1</sup>. This 3.3V can be enough to supply the circuit. You can see the circuit of the step-up converter in figure 4.2.

Figure 4.2: Step-up converter (1.2V to 3.3V)

We have to put some components around the MCP 1640 chip. The input capacitor of 4.7  $\mu$ F is recommended to decouple the voltage source. For low power applications, this capacitance is sufficient at the input. We have to use an X5R ceramic capacitor with a low ESR. The inductor of 4.7  $\mu$ H is an essential element for a step-up converter. It is a buffer for electrical energy and it is needed if we want a higher output voltage than the input voltage. To achieve a high efficiency, we also need an inductor with a low ESR. To calculate the values of the resistors (voltage divider), the datasheet gives the formula:

$$R_{TOP} = R_{BOTTOM} \cdot (\frac{V_{OUT}}{V_{FB}} - 1)$$

If we want  $V_{OUT}=3.3$  V, and with  $V_{FB}=1.21$  V and  $R_{BOTTOM}=300$  k $\Omega$ , we find:  $R_{TOP}=518.18$  k $\Omega\approx510$  k $\Omega$ .

The output capacitor of  $10 \mu F$  ensures a stable output voltage during sudden load transients and reduces the voltage ripple. To have a low ripple, we need a condensator with a low ESR. Again, we can use an X5R ceramic capacitor.

The question is now whether this voltage is enough to supply the op-amps we will use in our circuitry. So, we first searched for the op-amps and see what supply they need. We chose the AD817AN op-amp (see further). This op-amp cannot be supplied with a single 3.3 volt. We supplied it with a single 5 volt. Another way to supply the circuit had to be used.

We also found a step-up converter to boost 1.2 volt to 5 volt (see below). When we build the

http://wwl.microchip.com/downloads/en/DeviceDoc/22234B.pdf

circuit on a breadboard (with low ESR inductor and short connections), the circuit worked when there was no load. Once we connected the receiver, the voltage dropped to 3.5 volt what is not enough to supply our circuit. The step-up converter can't deliver enough current for a proper working of the receiver circuit.

**Figure 4.3:** Step-up converter (1.2V to 5V)

Then we tried to feed our circuit with the 5 volt from the USB port. This power supply is inherently unstable and depends on the load of the computer. Normally the supply can vary between 4.75 and 5.25 volt. But it can also be possible that the voltage drops to 4.4 volt or even lower. When we tried this to power our circuit, it worked. This 5 volt is used to supply the op-amps. This supply is not so critical, so our circuit will also work properly even if we don't have a stable supply voltage.

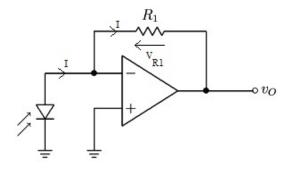

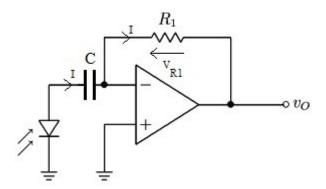

# 4.3 Current-voltage converter

To convert the current from the photodiode in a voltage, we have to use a current-voltage converter. A common way to do this, is to use an op-amp for it, as shown in figure 4.4. In an ideal op-amp the voltage on the minus pin is the same as the voltage on the plus pin. So, the photodiode is in short circuit. If we look to the graph of the short circuit current vs. illuminance (see figure 6.5), we see that the current is proportional to the incoming light if the photodiode is in short circuit.

To have an idea about the current through the photodiode and the voltage after the I-V converter, we set up the circuit of figure 4.4 (with  $R_1 = 100 \text{ k}\Omega$ , an LM324 op-amp and the BPW21R photodiode) on a breadboard and did some measurements. To determine the current, we can measure the voltage across the resistor. First, we looked what the voltage was in the office with infalling sunlight and with a fluorescent lamp at about two metres from the photodiode ( $V_{R1,light}$ ). Then, we looked what the voltage was when no light was falling on the diode,  $V_{R1,no-light}$ . We found:

Figure 4.4: Current-voltage converter

$$V_{R1,no-light} \approx 5 \text{ mV}$$

The current through the photodiode is (almost) equal to the current through  $R_1$ :

$$I_{light} = \frac{0.3V}{100k\Omega} = 3 \mu A$$

$$I_{no-light} = \frac{5mV}{100k\Omega} = 50 \text{ nA}$$

The output voltage  $V_O = -V_{R1}$ .

$$V_{R1,light} \approx -0.3 \text{ V}$$

$V_{R1,no-light} \approx -5 \text{ mV}$

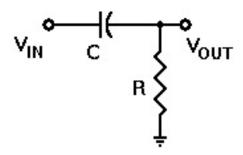

# 4.4 Ambient light filter

The photodiode will also pick up ambient light and light coming from the lighting in the building. Those have to be filtered out. The lighting in the building are fed from the net of 230  $V_{RMS}$  at 50 Hz. Due to the rectification, there will be radiation of 100 Hz frequency components that can influence the working of the photodiode. So, we need a high pass filter with a cut-off frequency  $f_{cut-off}$  above 100 Hz to filter the ambient light and the components of 100 Hz. Our first thought was to build a simple RC high pass filter (see figure 4.5) after the current-voltage converter. [2]

The formula for  $f_{cut-off}$  is then as follows:

$$f_{\text{cut-off}} = \frac{1}{2 \cdot \pi \cdot R \cdot C}$$

Figure 4.5: RC high pass filter

If we take  $f_{cut-off}$ =200 Hz and R=100  $\Omega$ , then we find: C=7,9577  $\mu$ F. We take the standard value C=10  $\mu$ F.

The cut-off frequency becomes:  $f_{\text{cut-off}}=159,155$  Hz. This value is good to filter the unwanted light.

If we make the circuit, the results are very poor. The bandwidth of the photodiode is large enough for the 100 kHz signal, so the problem must be something else. The characteristics of the LM324 op-amp aren't good enough for a square wave of 100 kHz. Two important characteristics of an op-amp are the bandwidth and the slew-rate. We found for the LM324 op-amp:

• Bandwidth: 1 MHz

• Slew rate:  $0.4 \frac{V}{\mu s}$

If we use another op-amp (AD817AN), the results are better:

• Bandwidth: 50 MHz

• Slew rate:  $350 \frac{V}{\mu s}$

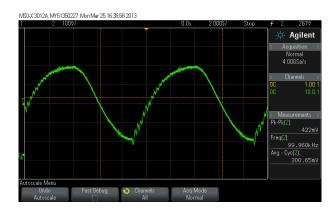

In first instance, the op-amp is supplied with  $\pm$  15 volt. If we switch the LED on and off at 100 kHz, we get a signal at the output of the receiver as you can see in figure 4.6.

We can see that the DC component is filtered out, but there is oscillation at the transition from low to high, so the circuit is not ideal to filter the ambient light.

Another thought for the filtering was to put a capacitor (10 nF) between the photodiode and the minus pin of the op-amp as you can see in figure 4.7.

Now we get a signal like you can see in figure 4.8.

The signal is better, but we can still see some high frequency components in the signal. The original rectangular shape is not so good visible anymore, the edges are flattened.

We chose to look for another way to filter the ambient light. After some research we

Figure 4.6: Output receiver with RC-filter

Figure 4.7: Ambient light filter circuit with capacitor

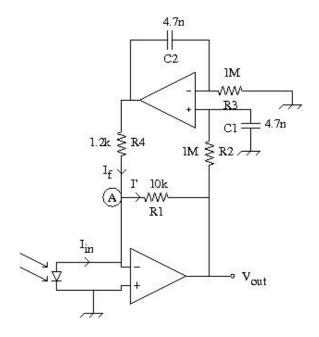

came to the circuit of figure 4.9. We use a feedback circuit that cancels out frequency components below a certain frequency. You can find more explanation about the circuit and the calculation of the transfer function and the cut-off frequency in appendix C.

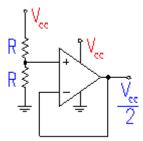

Until now, we always supplied the op-amps with  $\pm$  15 volt. We need three connectors to provide this supply. It should be easier to work with a single supply so we just need two connectors. Since we want to make a portable device, we will use lower voltages. The AD817AN op-amp needs at least a 5 volt single supply, so we will use this voltage to feed the op-amps.

Figure 4.8: Output receiver with condensator

Figure 4.9: Receiver circuit

By using a single positive supply, negative voltages cannot be generated. We will use a virtual ground instead of the normal ground. This special *ground* is usually a voltage reference half way between 0 volt and the supply voltage. In our case, the virtual ground will be 2.5 volt and can be made with a voltage divider and a voltage follower as shown in figure 4.10. [10]

Now we can just use this virtual ground instead of the normal ground. If we want to go

Figure 4.10: Creating a virtual ground for single supply operation

from dual to single supply operation, we have to replace the normal ground by the virtual ground.

# 4.5 Amplifier

Since the signal is too weak after filtering, we will use an amplifier. The amplification is needed if we want to use the full range of the ADC. After some measurements, we took an inverting op-amp with a gain of 100. Before the amplifier we put a high pass filter with  $f_{cut-off} = \frac{1}{2 \cdot \pi \cdot 5100 \cdot 10 \cdot 10^{-9}} = 31.2$  Hz and a gain of 1. We did this because we still had an offset after the ambient light rejection circuit. We also tried to use two op-amp stages with each a gain of 10, but the results weren't so good. We still had an offset and there was more noise in the signal. So, we decided to use a high pass filter with a gain of 1 and an inverting amplifier with a gain of 100.

When we simulated the ambient light rejection circuit, no offset was visible. We just had a DC offset of 2.5 volt because we are working with a virtual ground.

We also tried to build a high pass filter with a gain of 100, but an offset was still visible.

# 4.6 Anti-aliasing filter

It is recommended to use a low pass filter before the ADC to prevent aliasing. The Nyquist theorem says that the sample rate must be minimum twice the highest frequency component in the analog signal, if we want to reconstruct it properly. As we want to sample at 1 MHz, we will use a filter with a cut-off frequency of maximum 500 kHz.

The easiest and most common way to make a low pass is just to use a simple RC filter. In this case, it's not a good idea. RC filters are cheap, but at higher frequencies LC filters are a better choice. LC filters don't make use of resistors, so they don't dissipate power (in the ideal situation). We want a high order low pass filter with a steep attenuation curve to prevent aliasing. We chose to work with a 7th order filter (4 inductors and 3 capacitors) to have enough attenuation at 1 MHz. A 7th order filter has an attenuation of  $7 \cdot 20 \frac{dB}{dec} =$

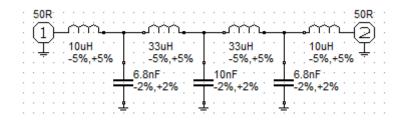

140  $\frac{dB}{dec}$ . To calculate the values of the components, we used the program *RFSim99* at the recommendation of Mr Rieder Médard. In this program we can calculate and simulate the filter we need. We have to give the filter type (Butterworth or Chebyshev), the cut-off frequency, the order of the filter and the input and output impedance. We chose for a 7th order Butterworth filter with a cut-off frequency of 500 kHz and an input and output impedance of 50  $\Omega$ . In the beginning, we chose this impedance because the spectrum can be easily measured with a network analyzer (optimized for input and output impedance of 50  $\Omega$ ). Later on, we replaced the input and output impedance with these of our circuit and looked how the spectrum of the filter changed. Once we have the calculated values, we took the nearest standard values. Finally, we had a result as you can see in figure 4.11.

**Figure 4.11:** LC filter with  $f_{cut-off} = 500$  kHz and  $Z_{in} = Z_{out} = 50 \Omega$

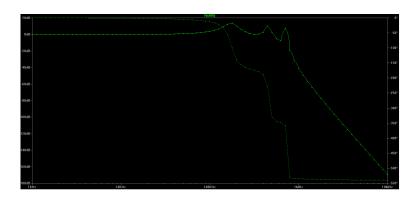

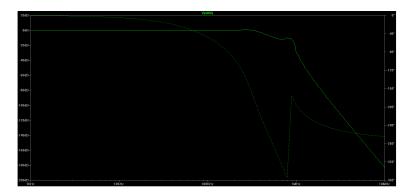

With the help of Mr Rieder Médard, we built the filter (figure 4.12) and measured the frequency spectrum of the filter with a network analyzer. The result can you see in figure 4.13. We can see that the filter is ideal to prevent anti-aliasing. We have a cut-off frequency (3 dB attenuation) of 474 kHz and at 1 MHz (sample rate), we have an attenuation of 36 dB.

**Figure 4.12:** LC filter with  $f_{cut-off} = 500$  kHz and  $Z_{in} = Z_{out} = 50 \Omega$  (PCB)

The problem is that the output and input impedance of the filter is supposed to be 50  $\Omega$ . In our circuit, this is not the case. The question is how the filter will react if we deviate from

**Figure 4.13:** Spectrum LC filter measured with network analyzer (50  $\Omega$  input and output impedance)

these impedances. The input impedance in our circuit is low ( $\approx 1~\Omega$ ), because the filter comes after an op-amp stage. The output impedance is determined by the voltage divider to buffer the ADC and is about 300  $\Omega$ . We simulated the filter with LT Spice with those impedances and had a look at the frequency spectrum (figure 4.14). We can see that there are some peaks above 0 dB in the spectrum which can cause oscillation. Nevertheless, we built the filter on a PCB to see what it gives. To built a good filter, it is also important to use inductors and capacitors with a low ESR so the losses are as low as possible.

**Figure 4.14:** Simulation spectrum LC filter with  $Z_{in} = 1 \Omega$  and  $Z_{out} = 300 \Omega$

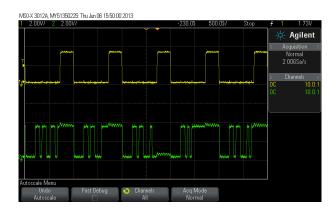

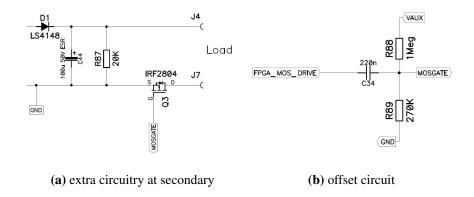

We made the whole circuitry an a PCB (from the photodiode to the ADC) and had a look at

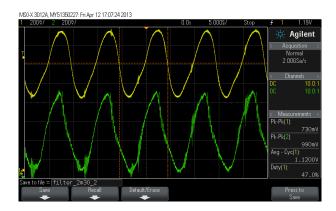

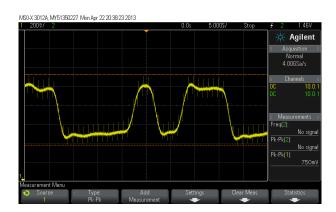

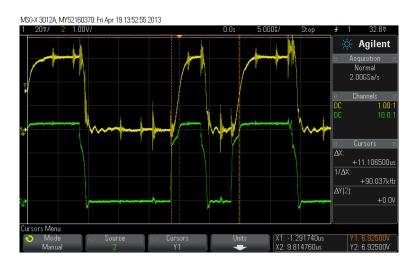

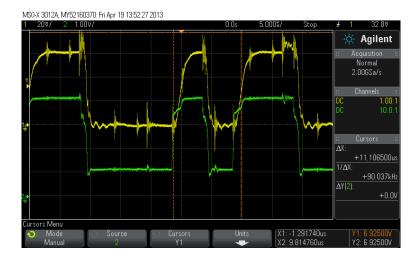

the signal before and after the filter (after the voltage divider). First, we switched the light on and off on the rhythm of a 100 kHz square wave at a distance between the LED and the receiver of 2,3 m. The results are shown in the picture below. The green curve represents the signal before the filter and the yellow curve after the filter. As you can see, the high frequency components and the noise are filtered out. The square wave has become almost a sine wave.

Figure 4.15: Signal before and after filter at 2,3 m (square wave)

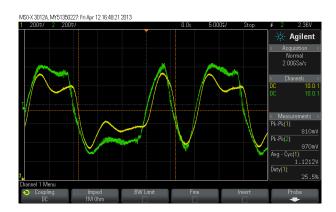

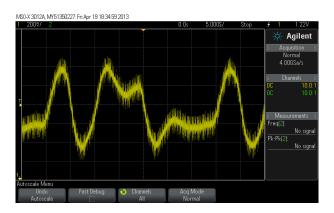

If we want to see for oscillation, we drive the LED with a 3-bit LFSR as discussed in chapter 3. Now we can see some oscillation in the signal. If the signal goes from low to high or vice versa, an overshoot occurs. As this is not very desirable, we tried to rebuilt the filter.

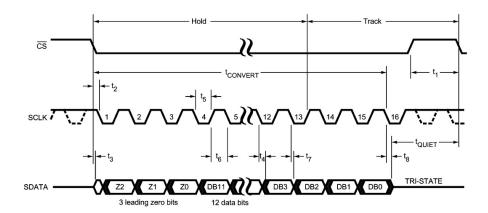

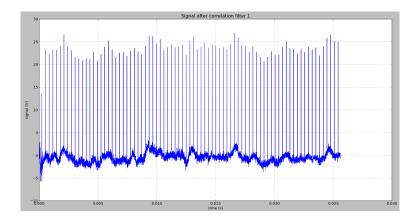

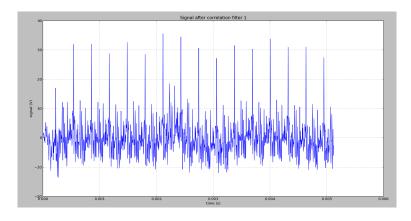

Figure 4.16: Signal before and after filter at 2,3 m (LFSR)